V kombinačních obvodech se k návrhu kodéru, multiplexeru, dekodéru a de-multiplexeru používají různé logické brány. Tyto obvody mají některé charakteristiky, například výstup tohoto obvodu závisí hlavně na úrovních, které jsou kdykoli na vstupních svorkách. Tento obvod neobsahuje žádnou paměť. Předchozí stav vstupu nemá žádný vliv na aktuální stav tohoto obvodu. Vstupy a výstupy kombinačního obvodu jsou „n“ č. vstupů a „m“ č. výstupů. Některé z kombinačních obvodů jsou poloviční sčítačka a plná sčítačka, odečítač, kodér, dekodér, multiplexor a demultiplexor. Tento článek pojednává o přehledu polovičního a plného sčítače a jeho práci s tabulkami pravdy.

Co je zmije?

Zmije je a digitální logický obvod v elektronice, která se ve velké míře používá k přidávání čísel. V mnoha počítačích a jiných typech procesorů se přidávače dokonce používají k výpočtu adres a souvisejících aktivit a k výpočtu indexů tabulky v ALU a dokonce se používají v jiných částech procesorů. Mohou být vytvořeny pro mnoho číselných reprezentací, jako je přebytek-3 nebo binárně kódované desetinné místo. Přidávače jsou v zásadě rozděleny do dvou typů: Half Adder a Full Adder.

Co je obvod napůl zmije a plný sčítač?

Poloviční sčítací obvod má dva vstupy: A a B, které přidávají dvě vstupní číslice a generují přenos a součet. Obvod plného sčítače má tři vstupy: A a C, které přidávají tři vstupní čísla a generují přenos a součet. Tento článek poskytuje podrobné informace o tom, co je účelem poloviční zmije a plná sčítačka v tabulkových formách a dokonce i v obvodových schématech. Již bylo zmíněno, že hlavním a zásadním účelem doplňků je přidání. Níže jsou uvedeny podrobné informace poloviční a plná zmije.

Základní poloviční zmije a plná zmije

Napůl zmije

Když tedy přijdeme ke scénáři poloviční sčítačky, přidá dvě binární číslice, kde jsou vstupní bity označovány jako augend a addend a výsledkem budou dva výstupy, jeden je součet a druhý je carry. Chcete-li provést součtovou operaci, XOR se použije na oba vstupy a AND brána se použije na oba vstupy, aby se vytvořil přenos.

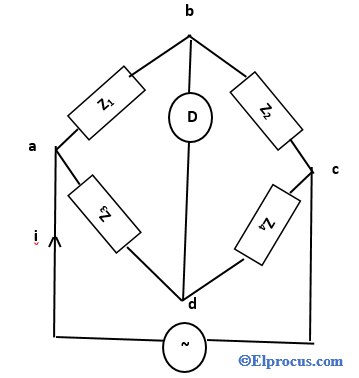

Funkční diagram HA

Zatímco v obvodu plného sčítače přidává 3 jednobitová čísla, kde dva ze tří bitů lze označovat jako operandy a druhý je označován jako bit nesený. Produkovaný výstup je 2bitový a lze je odkazovat jako výstup a součet.

Pomocí poloviční sčítačky můžete navrhnout jednoduché doplnění pomocí logických bran.

Podívejme se na příklad přidání dvou samostatných bitů.

2-bit poloviční sčítací tabulka pravdy je níže:

Tabulka pravdy poloviční zmije

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1

1 + 1 = 10

Toto jsou nejméně možné jednobitové kombinace. Ale výsledek pro 1 + 1 je 10, výsledek součtu musí být přepsán jako 2-bitový výstup. Rovnice lze tedy psát jako

0 + 0 = 00

0 + 1 = 01

1 + 0 = 01

1 + 1 = 10

Výstup „1“ z 10 je realizován. „SUM“ je normální výstup a „CARRY“ je provedení.

Nyní bylo jasné, že 1bitový sčítač lze snadno implementovat pomocí brány XOR pro výstup „SUM“ a brány AND pro „Carry“.

Například, když potřebujeme přidat dva 8bitové bajty dohromady, pak to lze implementovat pomocí logického obvodu s plným sčítačem. Poloviční sčítač je užitečný, když chcete přidat jednu binární číslici.

Způsob, jak vyvinout sčítače dvou binárních číslic, by bylo vytvořit tabulku pravdivosti a snížit ji. Pokud chcete vytvořit sčítač se třemi binárními číslicemi, operace přidání poloviny sčítače se provede dvakrát. Podobným způsobem, když se rozhodnete vytvořit čtyřciferný sčítač, operace se provede ještě jednou. S touto teorií bylo jasné, že implementace je jednoduchá, ale vývoj je časově náročný proces.

Nejjednodušší výraz používá exkluzivní funkci OR:

Součet = A XOR B

Carry = A AND B

Logický diagram HA

A ekvivalentní výraz, pokud jde o základní AND, OR a NOT, je:

SUM = A.B + A.B ‘

Kód VHDL pro poloviční zmije

Subjekt ha je

Port (a: v STD_LOGIC

b: v STD_LOGIC

sha: out STD_LOGIC

cha: out STD_LOGIC)

konec ha

Architektura Chování výše uvedeného obvodu je

začít

sha<= a xor b

Ne<= a and b

konec Behaviorální

Poloviční zmije IC číslo

Implementaci polovičního sčítače lze provést pomocí vysokorychlostních integrovaných obvodů digitální logiky CMOS, jako je řada 74HCxx, která zahrnuje SN74HC08 (7408) a SN74HC86 (7486).

Poloviční zmije omezení

Hlavním důvodem pro volání těchto binárních sčítačů jako Half Adders je, že neexistuje žádný rozsah pro zahrnutí bitového nosiče s použitím dřívějšího bitu. Toto je tedy hlavní omezení HA, které se kdysi používaly jako binární sčítač, zejména v situacích v reálném čase, které zahrnují přidání několika bitů. Toto omezení lze tedy překonat pomocí úplných doplňků.

Plná zmije

Tuto sčítačku je obtížné implementovat ve srovnání s poloviční sčítačkou.

Funkční schéma plného sčítače

Rozdíl mezi poloviční sčítačkou a plnou sčítačkou spočívá v tom, že plná sčítačka má tři vstupy a dva výstupy, zatímco poloviční sčítačka má pouze dva vstupy a dva výstupy. První dva vstupy jsou A a B a třetí vstup je vstup nesoucí jako C-IN. Když je navržena logika s plným sčítačem, osm z nich spojíte dohromady, abyste vytvořili sčítač po celém bajtu a kaskádovali bit přenášení z jednoho sčítače do druhého.

Tabulka pravdy FA

Výstupní přenos je označen jako C-OUT a normální výstup je reprezentován jako S, což je „SUM“.

S výše uvedeným plná tabulka pravdivosti zmije , implementaci celého obvodu sčítačky lze snadno pochopit. SUM „S“ se vyrábí ve dvou krocích:

- XORingem poskytované vstupy „A“ a „B“

- Výsledek A XOR B je poté XOR s C-IN

To generuje SUM a C-OUT je pravdivý pouze tehdy, když jsou dva ze tří vstupů VYSOKÉ, pak bude C-OUT VYSOKÝ. Můžeme tedy implementovat celý obvod sčítačky pomocí dvou obvodů sčítačky. Zpočátku bude poloviční sčítač použit k přidání A a B k vytvoření částečného součtu a logika sčítače druhé poloviny může být použita k přidání C-IN k součtu vytvořenému sčítačem první poloviny k získání konečného výstupu S.

Pokud některá z logik poloviční sčítačky vytvoří přenos, dojde k výstupu. C-OUT bude tedy funkcí NEBO výstupů přenosu poloviny sčítače. Níže se podívejte na implementaci celého obvodu zmije.

Logický diagram celého zmije

Implementace větších logických diagramů je možná s výše uvedenou úplnou logikou sčítače a pro reprezentaci operace se většinou používá jednodušší symbol. Níže je uvedeno jednodušší schematické znázornění jednobitového úplného sčítače.

S tímto typem symbolu můžeme přidat dva bity dohromady, přičemž vezmeme přenos z dalšího nižšího řádu a pošleme přenos do dalšího vyššího řádu. V počítači pro vícebitovou operaci musí být každý bit reprezentován plným sčítačem a musí být přidán současně. Chcete-li tedy přidat dvě 8bitová čísla, budete potřebovat 8 úplných doplňků, které lze vytvořit kaskádováním dvou ze 4bitových bloků.

Poloviční zmije a plná zmije pomocí K-Map

Dokonce i součet a nosné výstupy pro poloviční sčítačky lze získat také metodou Karnaughovy mapy (K-mapa). The poloviční sčítač a plný sčítač booleovský výraz lze získat prostřednictvím K-mapy. Níže je popsána K-mapa pro tyto doplňky.

Poloviční zmije K-mapa je

HA K-mapa

Plná zmije K-Map je

FA K-mapa

Logické vyjádření SUM a Carry

Logické vyjádření součtu (S) lze určit na základě vstupů uvedených v tabulce.

= A’B’Cin + A ’B CCin’ + A B’Cin ’+ AB Cin

= Cin (A’B ’+ AB) + Cin’ (A’B + A B ’)

= Cin EX-OR (A EX-OR B)

= (1,2,4,7)

Logický výraz carry (Cout) lze určit na základě vstupů uvedených v tabulce.

= A’B Cin + AB’Cin + AB Cin ‘+ ABCin

= AB + BCin + ACin

= (3, 5, 6, 7)

S výše uvedenými tabulkami pravdy lze získat výsledky a postup je následující:

Kombinovaný obvod kombinuje různé brány v obvodu, kde mohou být kodér, dekodér, multiplexer a demultiplexer . Vlastnosti kombinačních obvodů jsou následující.

- Výstup kdykoli je založen pouze na úrovních, které jsou přítomny na vstupních svorkách.

- Nepoužívá žádnou paměť. Předchozí stav vstupu nemá žádný vliv na současný stav obvodu.

- Může mít libovolný počet vstupů am počet výstupů.

Kódování VHDL

VHDL kódování pro plnou sčítačku zahrnout následující.

entita full_add je

Port (a: v STD_LOGIC

b: v STD_LOGIC

cin: v STD_LOGIC

součet: out STD_LOGIC

cout: out STD_LOGIC)

konec full_add

Chování architektury full_add je

složka ha je

Port (a: v STD_LOGIC

b: v STD_LOGIC

sha: out STD_LOGIC

cha: out STD_LOGIC)

koncová součást

signál s_s, c1, c2: STD_LOGIC

začít

HA1: mapa přístavů ha (a, b, s_s, c1)

HA2: mapa přístavů ha (s_s, cin, sum, c2)

náklady<=c1 or c2

konec Behaviorální

The rozdíl mezi poloviční a plnou sčítačkou je, že poloviční sčítačka produkuje výsledky a plná sčítačka používá poloviční sčítač k dosažení nějakého jiného výsledku. Podobně, zatímco Full-Adder je ze dvou Half-Adders, Full-Adder je skutečný blok, který používáme k vytvoření aritmetických obvodů.

Noste doplňky Lookahead

V koncepci obvodů sčítače hromadného přenosu jsou bity, které jsou nezbytné pro přidání, okamžitě k dispozici. Zatímco každá sčítací sekce musí mít svůj čas na příchod carry z předchozího sčítacího bloku. Z tohoto důvodu výroba SUM a CARRY zabere více času, protože každá sekce v obvodu čeká na příchod vstupu.

Například pro doručování výstupu pro n-tý blok potřebuje přijímat vstup z (n-1) tého bloku. A toto zpoždění se odpovídajícím způsobem nazývá zpoždění šíření.

Aby bylo možné překonat zpoždění ve zvlnění nese zmije, byla zavedena sčítačka carry-lookahead. Zde lze pomocí komplikovaného hardwaru minimalizovat zpoždění šíření. Níže uvedený diagram ukazuje sčítač carry-lookahead s využitím plných doplňků.

Noste Lookahead pomocí plné zmije

Pravdivostní tabulka a odpovídající výstupní rovnice jsou

| NA | B | C | C + 1 | Stav |

| 0 | 0 | 0 | 0 | No Carry generovat |

| 0 | 0 | 1 | 0 | |

| 0 | 1 | 0 | 0 | |

| 0 | 1 | 1 | 1 | No Carry Propagovat |

| 1 | 0 | 0 | 0 | |

| 1 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 1 | Nést generovat |

| 1 | 1 | 1 | 1 |

Nosná rovnice šíření je Pi = Ai XOR Bi a generování přenosu je Gi = Ai * Bi. S těmito rovnicemi lze rovnice součtu a přenášení reprezentovat jako

SUM = Pi XOR Ci

Ci + 1 = Gi + Pi * Ci

Gi přináší přenos pouze v případě, že oba vstupy Ai a Bi jsou 1, bez ohledu na přenos přenosu. Pi souvisí s šířením přenosu z Ci na Ci + 1.

Rozdíl mezi poloviční a plnou sčítačkou

The rozdíl mezi tabulkou polovičního a úplného sčítače je zobrazen níže.

| Napůl zmije | Plná zmije |

| Half Adder (HA) je kombinační logický obvod a tento obvod se používá k přidání dvou jednobitových číslic. | Full Adder (FA) je kombinační obvod a tento obvod se používá k přidání tří jednobitových číslic. |

| V HA nelze generovat carry z předchozího přidání do dalšího kroku. | Ve FA, jakmile je přenos vygenerován z dřívějšího přidání, může být přidán do dalšího kroku. |

| Poloviční zmije obsahuje dvě logické brány jako brána AND a brána EX-OR. | Plná sčítačka zahrnuje dvě brány EX-OR, dvě brány OR a dvě brány AND. |

| Vstupní bity v polovině sčítače jsou dva jako A, B. | Vstupní bity v úplném sčítači jsou tři jako A, B & C-in |

| Poloviční sčítací součet a přenosová rovnice je S = a⊕b C = a * b | Úplný sčítací logický výraz je S = a ⊕ b⊕Cin Cout = (a * b) + (Cin * (a⊕b)). |

| HA se používá v počítačích, kalkulačkách, zařízeních používaných pro digitální měření atd. | FA se používá v digitálních procesorech, přidávání více bitů atd. |

The klíčové rozdíly mezi poloviční a plnou sčítačkou jsou diskutovány níže.

- Poloviční sčítač generuje součet a přenos přidáním dvou binárních vstupů, zatímco celá sčítačka se používá ke generování součtu a přenosu přidáním tří binárních vstupů. Hardwarová architektura polovičního i úplného zmije není stejná.

- Hlavním rysem, který odlišuje HA & FA je, že v HA neexistuje žádná taková dohoda, která by považovala poslední přírůstek za jeho vstup. FA ale vyhledá konkrétní vstupní sloupec, jako je Cin, aby zvážil nosný bit posledního přírůstku.

- Dva sčítače ukáží rozdíl na základě komponent použitých v obvodu pro jeho konstrukci. Poloviční sčítače (HA) jsou navrženy s kombinací dvou logických bran jako AND & EX-OR, zatímco FA je navrženo s kombinací tří AND, dvou XOR a jedné brány OR.

- V zásadě fungují HA na 2-dvou vstupech po 1 bitech, zatímco FA fungují na třech vstupech po 1 bitech. Poloviční sčítač se používá v různých elektronických zařízeních k vyhodnocení přidání, zatímco plný sčítač se používá v digitálních procesorech pro přidání dlouhého bitu.

- Podobnosti v těchto dvou doplňcích jsou, že HA i FA jsou kombinační digitální obvody, takže nepoužívají žádný paměťový prvek, například sekvenční obvody. Tyto obvody jsou nezbytné pro aritmetický provoz k zajištění sčítání binárního čísla.

Plná implementace sčítače pomocí polovičních doplňků

Implementaci FA lze provést pomocí dvou polovičních sčítačů, které jsou logicky připojeny. Níže je uvedeno blokové schéma, které ukazuje připojení FA pomocí dvou polovičních sčítačů.

Rovnice součtu a přenosu z předchozích výpočtů jsou

S = A „B“ Cin + A „BC“ v + ABCin

Cout = AB + ACin + BCin

Součtovou rovnici lze zapsat jako.

Cin (A’B ‘+ AB) + C’ in (A’B + A B ’)

Takže Sum = Cin EX-OR (A EX-OR B)

Cin (A EX-OR B) + C’in (A EX-OR B)

= Cin EX-OR (A EX-OR B)

Cout lze psát následovně.

COUT = AB + ACin + BCin.

Cout = AB + + zklamání BCin (A + A)

= ABCin + AB + ACin + A ’B Cin

= AB (1 + Cin) + ACin + A ‘B Cin

= A B + ACin + A ’B Cin

= AB + ACin (B + B ’) + A’ B Cin

= ABCin + AB + A’B Cin + A ’B Cin

= AB (Cin + 1) + A B Cin + A ‘B Cin

= AB + AB ‘Cin + A’ B Cin

= AB + Cin (AB ‘+ A’B)

Proto COUT = AB + Cin (A EX-OR B)

V závislosti na výše uvedených dvou součtových a nosných rovnicích lze obvod FA implementovat pomocí dvou HA a brány OR. Schéma zapojení plného sčítače se dvěma polovičními sčítači je znázorněno výše.

Plná zmije pomocí dvou polovičních sčítačů

Full Adder Design s využitím bran NAND

Brána NAND je jeden druh univerzální brány, která se používá k provedení jakéhokoli logického návrhu. Níže je uveden obvod FA se schématem hradel NAND.

FA pomocí brány NAND

FA je snadný jednobitový sčítač, a pokud chceme provést přidání n-bitů, pak n ne. ve formátu kaskádového připojení musí být použito jednobitových FA.

Výhody

The výhody poloviční a plné zmije zahrnout následující.

- Nejdůležitějším účelem poloviční sčítačky je přidat dvě jednobitová čísla

- Plné sčítače mají schopnost přidat bit, který je výsledkem předchozího sčítání

- S plným sčítačem lze implementovat klíčové obvody jako sčítač, multiplexer a mnoho dalších

- Plné obvody sčítače spotřebovávají minimální energii

- Výhody plné sčítačky oproti polovině sčítače jsou, že plná sčítačka se používá k překonání nevýhody sčítače poloviny, protože polovina sčítače se používá hlavně k přidání dvou 1bitových čísel. Poloviční přidání nepřidá nosný bit, takže k překonání tohoto plného zmije se používá. V úplném sčítači lze provést přidání tří bitů a vygeneruje dva výstupy.

- Návrh doplňků je jednoduchý a jedná se o základní stavební kámen, aby bylo snadno pochopitelné jednobitové přidání.

- Tuto sčítačku lze převést na poloviční odečítač přidáním invertoru.

- Použitím plného sčítače lze dosáhnout vysokého výkonu.

- Vysoká rychlost

- Velmi silné pro změnu měřítka napájecího napětí

Nevýhody

The nevýhody polovičního a plného zmije zahrnout následující.

- Poloviční sčítač navíc nelze použít před přenášením, takže není použitelný pro kaskádové přidání vícebitového.

- K překonání této nevýhody je nutné FA přidat 1 1 bit.

- Jakmile se FA použije ve formě řetězce jako RA (zvlnění), lze snížit výstupní kapacitu pohonu.

Aplikace

Mezi aplikace sčítače s poloviční a plnou sčítačkou patří následující.

- Přidání binárních bitů lze provést poloviční sčítačkou pomocí ALU v počítači, protože používá sčítač.

- Pro návrh celého obvodu sčítačky lze použít poloviční sčítací kombinaci.

- Poloviční sčítače se používají v kalkulačkách a pro měření adres i tabulek

- Tyto obvody se používají pro zpracování různých aplikací v digitálních obvodech. V budoucnu hraje klíčovou roli v digitální elektronice.

- Obvod FA se používá jako prvek v mnoha velkých obvodech, jako je Ripple Carry Adder. Tento sčítač přidává počet bitů současně.

- FA se používají v aritmetické logické jednotce (ALU)

- FA se používají v grafických aplikacích, jako je GPU (Graphics Processing Unit)

- Ty se používají v multiplikačním obvodu k provedení Carryout Multiplication.

- V počítači se k vygenerování adresy paměti a vytvoření kontrapunktu programu k následné instrukci používá aritmetická logická jednotka pomocí Full Adders.

Kdykoli je tedy provedeno přidání dvou binárních čísel, jsou číslice přidávány nejdříve nejméně bity. Tento proces lze provést pomocí poloviční sčítačky, protože nejjednodušší n / w, který umožňuje přidání dvou 1bitových čísel. Vstupy tohoto sčítače jsou binární číslice, zatímco výstupy jsou součet (S) a carry (C).

Kdykoli je zahrnut počet číslic, pak se síť HA používá jednoduše k připojení nejmenších číslic, protože HA nemůže přidat číslo přenosu z dřívější třídy. Plnou sčítačku lze definovat jako základ všech digitálních aritmetických zařízení. Slouží k přidání tří jednociferných čísel. Tento sčítač obsahuje tři vstupy jako A, B a Cin, zatímco výstupy jsou Sum a Cout.

Související pojmy

The koncepty související s poloviční a plnou sčítačkou prostě se nedržet jediného účelu. Mají rozsáhlé použití v mnoha aplikacích a je zmíněno několik souvisejících:

- Poloviční sčítač a plné IC číslo

- Vývoj 8bitového sčítače

- Jaká jsou preventivní opatření u poloviny zmije?

- JAVA applet zvlňovacího nosiče

Proto je to všechno o poloviční a plná zmije spolu s tabulkami pravdy a logickými diagramy je také zobrazen návrh plného sčítače s využitím obvodu sčítače s polovinou. Mnoho z poloviční sčítačka a plná sčítačka pdf jsou k dispozici dokumenty, které poskytují pokročilé informace o těchto konceptech. Je dále důležité vědět jak je implementována 4bitová plná sčítačka ?