The tranzistor s efektem pole (FET) je elektronické zařízení, ve kterém elektrické pole se používá k regulaci toku proudu. K realizaci tohoto je aplikován rozdíl potenciálů přes hradlové a zdrojové svorky zařízení, což mění vodivost mezi odtokovými a zdrojovými svorkami, což způsobuje, že přes tyto svorky protéká řízený proud.

FET se nazývají unipolární tranzistory protože jsou navrženy tak, aby fungovaly jako zařízení s jedním nosičem. K dispozici jsou různé typy tranzistorů s efektem pole.

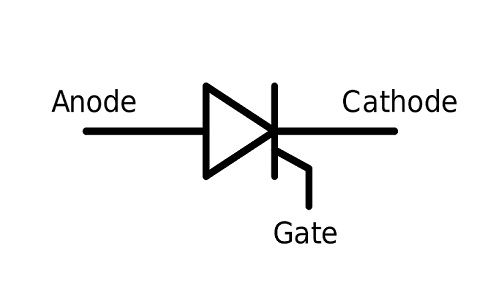

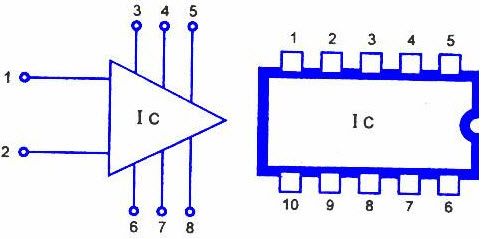

Symbol

Grafické symboly pro JFET kanálu n a kanálu p lze vizualizovat na následujících obrázcích.

Můžete si jasně všimnout, že značky šipek, které směřují dovnitř zařízení s n-kanálem, označují směr, kterým jáG(proud brány) má proudit, když křižovatka p-n byla předpjatá.

V případě zařízení s kanálem p jsou podmínky stejné, kromě rozdílu ve směru symbolu šipky.

Rozdíl mezi FET a BJT

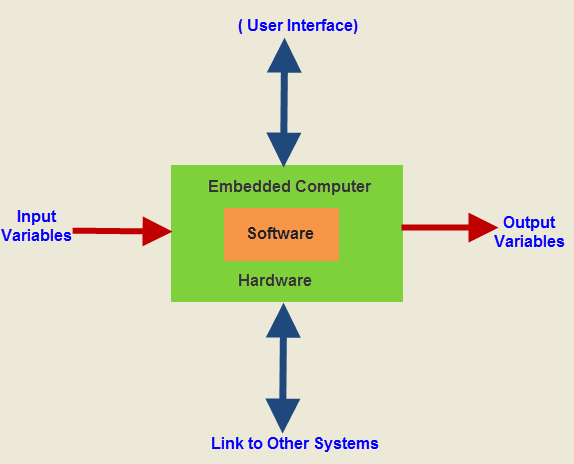

Tranzistor s polním efektem (FET) je tříkoncové zařízení určené pro širokou škálu obvodových aplikací, které na vysoké úrovni doplňují tranzistor BJT.

I když najdete významné odchylky mezi BJT a JFET, ve skutečnosti existuje několik charakteristik shody, o kterých bude řeč v následujících diskusích. Hlavní rozdíl mezi těmito zařízeními je BJT je zařízení řízené proudem, jak je znázorněno na obr. 5.1a, zatímco tranzistor JFET je zařízení řízené napětím, jak je znázorněno na obr. 5.1b.

Jednoduše řečeno, aktuální ICna obr. 5.1a je okamžitá funkce úrovně IB. Pro FET je proud I funkcí napětí VGSvzhledem ke vstupnímu obvodu, jak je znázorněno na obr. 5.1b.

V obou případech bude proud výstupního obvodu řízen parametrem vstupního obvodu. V jedné situaci úroveň proudu a v druhé aplikované napětí.

Stejně jako npn a pnp pro bipolární tranzistory najdete tranzistory s efektem n-kanálu a p-kanálu. Měli byste však pamatovat na to, že BJT tranzistor je bipolární zařízení s předponou bi-, což naznačuje, že úroveň vedení je funkcí dvou nosičů náboje, elektronů a děr.

FET na druhé straně je a unipolární zařízení to závisí pouze na vedení elektronu (n-kanál) nebo otvoru (p-kanál).

Slovní spojení „efekt pole“ lze vysvětlit takto: každý z nás si je vědom síly permanentního magnetu přilákat kovové piliny směrem k magnetu bez jakéhokoli fyzického kontaktu. Docela podobným způsobem uvnitř FET je elektrické pole vytvářeno existujícími náboji, které ovlivňují vodivou cestu výstupního obvodu, aniž by došlo k přímému kontaktu mezi řídicí a regulovanou veličinou. Pravděpodobně jednou z nejdůležitějších vlastností FET je jeho vysoká vstupní impedance.

V rozsahu od 1 do mnoha set megohmů výrazně překračuje rozsahy normálního vstupního odporu konfigurací BJT, což je mimořádně důležitý atribut při vývoji modelů lineárních střídavých zesilovačů.

Avšak BJT nese větší citlivost na změny vstupního signálu. To znamená, že změna výstupního proudu je obvykle významně více u BJT než FET u stejného rozsahu změny jejich vstupních napětí.

Z tohoto důvodu mohou být standardní přírůstky střídavého napětí pro zesilovače BJT mnohem vyšší ve srovnání s FET.

Obecně lze říci, že FET jsou podstatně tepelně odolnější než BJT a ve srovnání s BJT mají také často menší strukturu, díky čemuž jsou speciálně vhodné pro zabudování jako integrovaný obvod (IC)bramborové hranolky.

Na druhé straně strukturální charakteristiky některých FET mohou umožnit, aby byly na fyzické kontakty mimořádně citlivé než BJT.

Více vztahů BJT / JFET

- Pro BJT VBÝT= 0,7 V je důležitým faktorem pro zahájení analýzy jeho konfigurace.

- Podobně parametr IG= 0 A je obvykle první věc, která se uvažuje pro analýzu obvodu JFET.

- Pro konfiguraci BJT IBje často prvním faktorem, který je nutné určit.

- Podobně pro JFET je to obvykle VGS.

V tomto článku se zaměříme na JFET nebo tranzistory s efektem spojovacího pole, v dalším článku pojednáme o tranzistoru pole kov-oxid-polovodičové pole-efekt nebo MOS-FET.

KONSTRUKCE A CHARAKTERISTIKA JFET

Jak jsme se dozvěděli, sluchátko má JFET 3 vodiče. Jeden z nich řídí tok proudu mezi ostatními dvěma.

Stejně jako BJT, i v JFET je zařízení s n-kanálem používáno výrazněji než protějšky p-kanálu, protože n zařízení mají ve srovnání s p-zařízením tendenci být efektivnější a uživatelsky přívětivější.

Na následujícím obrázku vidíme základní strukturu nebo konstrukci n-kanálového JFET. Vidíme, že složení typu n tvoří hlavní kanál napříč vrstvami typu p.

Horní část kanálu typu n je spojena prostřednictvím ohmického kontaktu s terminálem s názvem odtok (D), zatímco spodní část stejného kanálu je také spojena prostřednictvím ohmického kontaktu s jiným terminálem s názvem zdroj (S).

Pár materiálů typu p je dohromady spojeno s terminálem označovaným jako brána (G). V podstatě zjistíme, že odtokové a zdrojové terminály jsou připojeny ke koncům kanálu typu n. Terminál brány je spojen s dvojicí materiálu p-kanálu.

Když na jfet není aplikováno žádné napětí, jeho dva p-n křižovatky jsou bez jakýchkoli ovlivňujících podmínek. V této situaci existuje oblast vyčerpání na každém spoji, jak je uvedeno na výše uvedeném obrázku, která vypadá docela jako oblast diod d-n bez předpětí.

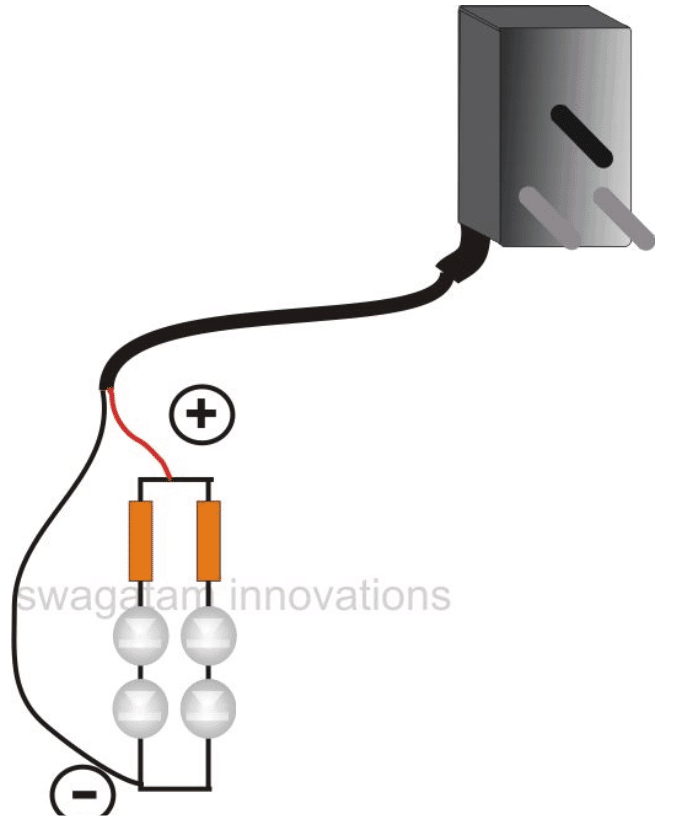

Analogie vody

Pracovní a kontrolní operace JFET lze pochopit pomocí následující analogie vody.

Zde lze porovnat tlak vody s velikostí aplikovaného napětí od odtoku ke zdroji.

Tok vody lze srovnávat s tokem elektronů. Ústí kohoutku napodobuje zdrojový terminál JFET, zatímco horní část kohoutku, do které je tlačena voda, zobrazuje odtok JFET.

Knoflíkový knoflík funguje jako brána JFET. Pomocí vstupního potenciálu řídí tok elektronů (náboj) z odtoku ke zdroji, stejně jako knoflík ovládá tok vody na otvoru úst.

Ze struktury JFET vidíme, že odtokové a zdrojové terminály jsou na opačných koncích n-kanálu, a protože tento termín je založen na elektronovém toku, můžeme psát:

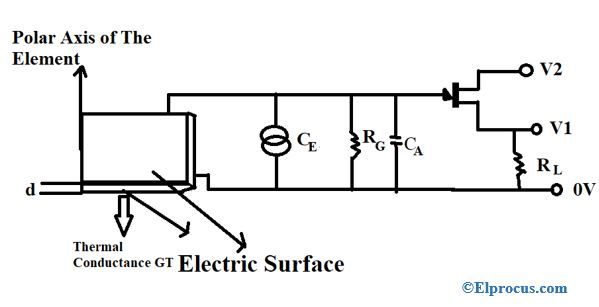

PROTIGS= 0 V, VDSNějaká pozitivní hodnota

Na obr. 5.4 vidíme kladné napětí VDSaplikován přes n-kanál. Terminál brány je přímo připojen ke zdroji, aby se vytvořila podmínka V.GS= 0V. To umožňuje, aby brána a zdrojové terminály byly na stejném potenciálu, a výsledkem je oblast vyčerpání dolního konce každého p-materiálu, přesně tak, jak vidíme v prvním diagramu výše, s podmínkou bez zkreslení.

Jakmile napětí VDD(= VDS), elektrony jsou taženy směrem k odtokovému terminálu a generují konvenční tok proudu ID, jak je uvedeno na obr. 5.4.

Směr toku náboje ukazuje, že odtokový a zdrojový proud mají stejnou velikost (ID= JáS). Podle podmínek znázorněných na obr. 5.4 vypadá tok vsázky zcela neomezeně a je ovlivněn pouze odporem n-kanálu mezi odtokem a zdrojem.

Můžete si všimnout, že oblast vyčerpání je větší kolem horní části obou materiálů typu p. Tento rozdíl ve velikosti regionu je ideálně vysvětlen na obr. 5.5. Představme si jednotný odpor v n-kanálu, který lze rozdělit na úseky uvedené na obr. 5.5.

Aktuální IDmůže vytvářet rozsahy napětí kanálem, jak je uvedeno na stejném obrázku. Ve výsledku bude horní oblast materiálu typu p obrácena předpětím o úroveň kolem 1,5 V, přičemž spodní oblast bude předpětí pouze o 0,5 V.

Bod, ve kterém je křižovatka p-n reverzně předpjatý podél celého kanálu, vede ke vzniku hradlového proudu s nulovými ampéry, jak je znázorněno na stejném obrázku. Tato vlastnost, která vede k IG= 0 A je důležitou charakteristikou JFET.

Jako VDSpotenciál je zvýšen z 0 na několik voltů, proud se zvyšuje podle Ohmova zákona a grafu IDřádek 5DSmůže vypadat jako osvědčený na obr. 5.6.

Srovnávací přímost vykreslování ukazuje, že pro oblasti s nízkou hodnotou VDS, odpor je v zásadě jednotný. Jako VDSstoupá a blíží se úrovni známé jako VP na obr. 5.6, oblasti vyčerpání se rozšiřují, jak je uvedeno na obr. 5.4.

To má za následek zjevné snížení šířky kanálu. Snížená dráha vedení vede ke zvýšení odporu, což vede ke křivce na obr. 5.6.

Čím je křivka vodorovnější, tím vyšší je odpor, což naznačuje, že odpor se v horizontální oblasti přibližuje k „nekonečným“ ohmům. Když VDSzvyšuje se do té míry, že by se mohlo zdát, že by obě oblasti vyčerpání mohly „kontaktovat“, jak je znázorněno na obr. 5.7, vede k situaci známé jako pinch-off.

Částka, o kterou VDSrozvíjí tato situace se nazývá pinch-off napětí a je symbolizováno V.Pjak je znázorněno na obr. 5.6. Slovo pinch-off je obecně zavádějící, protože implikuje aktuální IDje „sevřen“ a klesne na 0 A. Jak dokazuje obr. 5.6, v tomto případě to vypadá jen těžko. JáDzachovává úroveň sytosti charakterizovanou jako I.DSSna obr. 5.6.

Pravdou je, že stále existuje velmi malý kanál s proudem výrazně vysoké koncentrace.

Bod, ve kterém ID neklesá pinch-off a zachovává úroveň sytosti, jak je znázorněno na obr. 5.6, je potvrzeno následujícím důkazem:

Protože neexistuje žádný odběrový proud, vylučuje možnost různých úrovní potenciálu prostřednictvím materiálu n-kanálu pro určování měnících se množství zpětného zkreslení podél p-n spojení. Konečným výsledkem byla ztráta distribuce oblasti vyčerpání, která se spustila pinch-off začít.

Jak zvyšujeme VDSnad VP, oblast blízkého kontaktu, kde se obě oblasti vyčerpání setkají navzájem, se zvětšuje v délce podél kanálu. Úroveň ID se však v zásadě nemění.

Tedy okamžik VDSje vyšší než Vp, JFET získává charakteristiky zdroje proudu.

Jak je ukázáno na obr. 5.8, proud v JFET je určen na ID= JáDSS, ale napětí VDSvyšší než VP je stanoveno připojenou zátěží.

Výběr notace IDSS je založen na skutečnosti, že se jedná o proud typu Drain to Source, který má zkratovaný odkaz přes bránu ke zdroji.

Další vyšetřování nám dává následující hodnocení:

JáDSSje nejvyšší odběrový proud pro JFET a je stanoven podmínkami VGS= 0 V a VDS> | VP |.

Všimněte si, že na obr. 5.6 VGSje 0V pro kompletní úsek křivky. V následujících částech se dozvíme, jak jsou atributy obrázku 5.6 ovlivňovány jako úroveň VGSje pestrá.

PROTIGS <0V

Odchylka aplikovaná přes bránu a zdroj je označena jako VGS, která je zodpovědná za řízení operací JFET.

Vezmeme-li příklad BJT, stejně jako křivky ICvs VTENTOjsou určeny pro různé úrovně IBpodobně křivky IDvs VDSpro různé úrovně VGSlze vytvořit pro protějšek JFET.

Za tímto účelem je terminál brány nastaven na pokračující nižší potenciál pod úrovní zdrojového potenciálu.

S odkazem na obr. 5.9 níže je aplikováno -1V přes terminály brány / zdroje pro snížené VDSúroveň.

Cíl zaujatosti negativního potenciálu VGSje vyvinout regiony vyčerpání připomínající situaci V.GS= 0, ale při výrazně sníženém VDS.

To způsobí, že brána dosáhne bodu nasycení s nižšími úrovněmi VDSjak je uvedeno na obr. 5.10 (VGS= -1V).

Odpovídající úroveň saturace pro I.Dlze zjistit, že se zmenšuje a ve skutečnosti se stále snižuje jako VGSje negativnější.

Na obr. 5.10 můžete jasně vidět, jak odtrhávací napětí klesá při parabolickém tvaru jako VGSje stále negativnější.

Nakonec, když VGS= -Vp, bude dostatečně negativní, aby se stanovila úroveň nasycení, která je nakonec 0 mA. Na této úrovni je JFET zcela „vypnutý“.

Úroveň VGScož způsobuje IDpro dosažení 0 mA je charakterizováno VGS= VP, kde VPje záporné napětí pro n-kanálová zařízení a kladné napětí pro p-kanálové JFET.

Obvykle najdete většinu datových listů JFET pinch-off napětí specifikované jako VGS (vypnuto)místo VP.

Oblast na pravé straně odtrhovacího lokusu na výše uvedeném obrázku je místem, které se běžně používá v lineárních zesilovačích pro dosažení signálu bez zkreslení. Tato oblast se obecně nazývá oblast konstantního proudu, saturace nebo lineárního zesílení.

Napěťově řízený rezistor

Oblast, která je na stejné straně na levé straně odtrhovacího lokusu, se nazývá ohmická oblast nebo oblast odporu řízená napětím.

V této oblasti může být zařízení ve skutečnosti provozováno jako proměnný rezistor (například v aplikaci s automatickým řízením zisku), přičemž jeho odpor je řízen prostřednictvím použitého potenciálu brány / zdroje.

Vidíte, že sklon každé z křivek, který také značí odpor odtoku / zdroje JFET pro VDS

Jak děláme VGS vyšší s negativním potenciálem, sklon každé křivky se stává více a více horizontálním a vykazuje úměrně zvyšující se úrovně odporu.

Pomocí následující rovnice jsme schopni získat dobrou počáteční aproximaci úrovně odporu vzhledem k napětí VGS.

p-Channel JFET pracuje

Vnitřní rozvržení a konstrukce JFET s kanálem p jsou přesně identické s protějškem kanálu n, kromě toho, že oblasti materiálů typu p a n jsou obráceny, jak je znázorněno níže:

Směr toku proudu lze také považovat za obrácený spolu se skutečnou polaritou napětí VGS a VDS. V případě p-kanálu JFET bude kanál omezen v reakci na zvýšení pozitivního potenciálu přes bránu / zdroj.

Zápis s dvojitým dolním indexem pro VDSzpůsobí záporné napětí pro VDS, jak je znázorněno na charakteristikách obr. 5.12. Tady najdete IDSSpři 6 mA, zatímco odtrhávací napětí při VGS= + 6V.

Nenechte se zmást kvůli přítomnosti znaku mínus pro VDS. Jednoduše naznačuje, že zdroj nese vyšší potenciál než odtok.

Vidíte, že křivky pro vysoké VDSúrovně náhle vzrostou na hodnoty, které vypadají neomezeně. Indikovaný vzestup, který je svislý, symbolizuje situaci poruchy, což znamená, že proud v kanálovém zařízení je v tomto okamžiku zcela řízen vnějšími obvody.

Ačkoli to na obr. 5.10 u n-kanálového zařízení není patrné, může to být možnost při dostatečně vysokém napětí.

Tuto oblast lze vyloučit, pokud je VDS (max.)je zaznamenáno z datového listu zařízení a zařízení je nakonfigurováno tak, aby aktuální VDShodnota je nižší než tato zaznamenaná hodnota pro libovolné VGS.

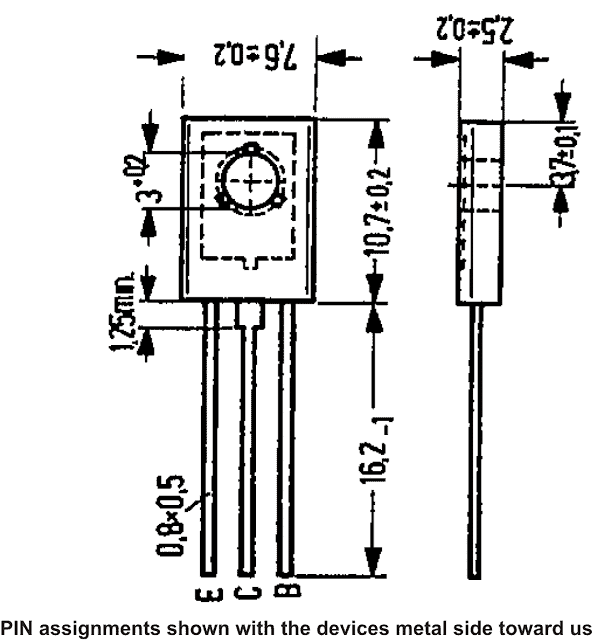

Dvojice: Prozkoumáno 5 nejlepších 40 Wattových zesilovacích obvodů Další: Datový list 2N3055, Pinout, aplikační obvody