V každodenním životě se setkáváme s různými typy elektronických gadgetů. Jednou z technologií, která přinesla revoluci ve výrobě elektroniky, je „ Integrovaný obvod “. Tato technologie snížila velikost elektronických výrobků zvýšením hustoty logické brány na čip. Dnes máme různé typy a konfigurace integrovaných obvodů. Jak pozorujeme kolem, zjistíme, že některé integrované obvody lze použít pouze pro jednu konkrétní aplikaci, zatímco některé integrované obvody lze přeprogramovat a použít pro různé aplikace. Tyto typy integrovaných obvodů jsou pojmenovány jako ASIC. Jak se ale liší? Jak je možné je přeprogramovat? Proč nelze některé integrované obvody přeprogramovat? Zkuste najít odpovědi na tyto otázky.

Co je ASIC (Application Specific Integrated Circuit)?

Plná forma ASIC je Integrovaný obvod specifický pro aplikaci. Tyto obvody jsou specifické pro konkrétní aplikaci, tj. IC na míru pro konkrétní aplikaci. Ty jsou obvykle navrženy z kořenové úrovně na základě požadavku konkrétní aplikace. Některé ze základních příklady integrovaných obvodů specifické pro konkrétní aplikaci jsou čipy používané v hračkách, čip používaný k propojení paměti a mikroprocesoru atd ... Tyto čipy lze použít pouze pro jednu aplikaci, pro kterou jsou určeny. Pravděpodobně tyto typy integrovaných obvodů jsou preferovány pouze u těch produktů, které mají velkou produkci. Protože ASIC jsou navrženy od kořenové úrovně, mají vysoké náklady a jsou doporučeny pouze pro velkoobjemové produkce.

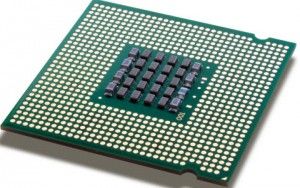

Hlavní výhodou ASIC je zmenšená velikost čipu, protože velké množství funkčních jednotek obvodu je konstruováno přes jeden čip. Moderní ASIC obecně obsahuje 32 bitů mikroprocesor , paměťové bloky, síťové obvody atd ... Takový typ ASIC je znám jako Systém na čipu . S rozvojem výrobní technologie a zvýšeným výzkumem v konstrukčních metodách se vyvíjejí ASIC s různými úrovněmi přizpůsobení.

Typy ASIC

ASIC jsou kategorizovány na základě rozsahu přizpůsobení, které má programátor na čipu povoleno.

Typy ASIC

Úplně vlastní

V tomto typu designu jsou všechny logické buňky šité na míru pro konkrétní aplikaci. Tj. Návrhář musí speciálně vytvořit logické buňky pro obvody. Všechny vrstvy masky pro propojení jsou přizpůsobeny. Programátor tedy nemůže měnit propojení čipu a při programování musí být obeznámen s uspořádáním obvodu.

Jedním z nejlepších příkladů Full custom ASIC je mikroprocesor. Tento typ přizpůsobení umožňuje návrhářům postavit různé analogové obvody, optimalizované paměťové buňky nebo mechanické struktury na jediném integrovaném obvodu. Výroba tohoto ASIC je nákladná a časově velmi náročná. Čas potřebný k návrhu těchto integrovaných obvodů je přibližně osm týdnů.

Obvykle jsou určeny pro aplikace na vysoké úrovni. Maximální výkon, minimalizovaná plocha a nejvyšší stupeň flexibility jsou hlavními rysy Full custom designu. Nakonec je riziko v konstrukci vysoké, protože logické články, rezistor atd.… Použité prvky obvodu nejsou předem testovány.

Polozvyk

V tomto typu designu jsou logické buňky převzaty ze standardních knihoven, tj. nejsou vyrobeny ručně jako v provedení Full custom. Některé masky jsou přizpůsobeny, zatímco některé jsou převzaty z předem navržené knihovny. Na základě typu logických buněk převzatých z knihovny a rozsahu přizpůsobení povoleného pro propojení jsou tyto ASIC rozděleny na dva typy - standardní ASIC založené na buňkách a ASIC založené na Gate Array.

1). Standardní buňkový ASIC

Abychom nejprve poznali tyto IC, pochopme, co znamená standardní buněčná knihovna. Některé z logických buněk, jako je A brány, NEBO brány , multiplexery, žabky jsou předem navrženy designéry používajícími různé konfigurace, standardizovány a uloženy ve formě knihovny. Tato kolekce je známá jako standardní knihovna buněk.

Standardní buňkový ASIC

Ve standardních buňkách jsou použity logické buňky ASIC z těchto standardních knihoven. Na čipu ASIC jsou standardní oblast buněk nebo flexibilní blok tvořeny standardními buňkami uspořádanými ve formě řádků. Spolu s těmito flexibilními bloky se na čipu používají mega buňky, jako jsou mikrokontroléry nebo dokonce mikroprocesory. Tyto mega buňky jsou také známé jako Mega funkce, makra na úrovni systému, pevné bloky, funkční standardní bloky.

Výše uvedený obrázek představuje standardní buňku ASIC s jedinou standardní oblastí buňky a čtyřmi pevnými bloky. Vrstvy masky jsou přizpůsobeny. Zde může návrhář umístit standardní buňky kamkoli na matrici. Tito jsou také známí jako C-BIC.

2). Gate Array Based ASIC

Tento typ semi-custom ASIC mají předdefinované tranzistory na křemíkové destičce. tj. návrhář nemůže změnit umístění tranzistorů přítomných na matrici. Základní pole je předdefinovaný vzor hradlového pole a základní buňka je nejmenší opakující se buňka základního pole.

Návrhář nese odpovědnost pouze za změnu propojení mezi tranzistory pomocí prvních několika kovových vrstev matrice. Návrhář si vybere z knihovny hradlového pole. Často se jim říká Masked Gate Array. Gate Array Based ASIC jsou tři typy. Jsou to Channeled Gate Array, Channel less gate array a strukturované hradlové pole.

a). Channeled Gate Array

U tohoto typu hradlového pole je mezi řadami tranzistorů ponechán prostor pro elektroinstalaci. Jsou podobné CBIC, protože je ponechán prostor pro propojení mezi bloky, ale v řádcích buněčných řádků pole pole jsou fixovány na výšku, zatímco v CBIC lze tento prostor upravit.

Channeled Gate Array

Některé z hlavních funkcí tohoto hradlového pole jsou - toto hradlové pole používá k propojení předdefinované mezery mezi řádky. Doba výroby je dva dny až dva týdny.

b). Channel Less Gate Array

Nezbývá žádné volné místo pro směrování mezi řadami buněk, jak je vidět v poli směrované brány. Zde se směrování provádí shora nad buňkami pole brány, protože můžeme přizpůsobit spojení mezi kovovou 1 a tranzistory. Pro směrování necháme tranzistory ležící v cestě směrování nevyužité. Doba výroby je asi dva týdny.

Channel Less Gate Array

C). Strukturované pole brány

Tento typ hradlového pole má vložený blok spolu s řádky hradlového pole, jak je vidět výše. Strukturované pole brány má vyšší plošnou účinnost CBIC. Stejně jako pole maskované brány mají i tyto nižší náklady a rychlejší zpracování. Zde pevná velikost vložené funkce představuje omezení pro pole strukturované brány. Například toto pole brány obsahuje oblast vyhrazenou pro 32k bitový řadič, ale pokud v aplikaci vyžadujeme pouze oblast pro 16k bitový řadič, zbylá oblast bude zbytečná. Všechna hradlová pole mají dobu obratu dva dny až dva týdny a všechny mají přizpůsobené propojení.

Strukturované pole brány

Programovatelný ASIC

Existují dva typy programovatelných ASIC. Jsou to PLD a FPGA

PLD (programovatelná logická zařízení)

Jedná se o standardní buňky snadno dostupné. Můžeme naprogramovat PLD na přizpůsobenou část aplikace, takže jsou považovány za ASIC. K programování PLD můžeme použít různé metody a software. Ty obsahují běžnou matici logických buněk obvykle programovatelnou logiku pole spolu s klopnými obvody nebo západkami. Zde jsou propojení přítomna jako jeden velký blok.

PROM je běžným příkladem tohoto IC. EPROM používá MOS tranzistory jako propojení, takže použitím vysokého napětí jej můžeme naprogramovat. PLD nemají žádné přizpůsobené logické buňky nebo se vzájemně propojují. Mají rychlý designový obrat.

Programovatelná logická zařízení

FPGA (Field Programmable Gate Array)

Kde PLD mají programovatelnou logiku pole jako logické buňky FPGA má uspořádání podobné branovému poli. PLD jsou menší a méně složité než FPGA. Díky své flexibilitě a vlastnostem nahrazuje FPGA TTL v mikroelektronických systémech. Návrhový obrat je jen pár hodin.

Polní programovatelné hradlové pole

Jádro se skládá z programovatelných základních logických buněk, které mohou provádět obojí kombinační a sekvenční logika . Můžeme naprogramovat logické buňky a propojit se pomocí některých metod. Základní logické buňky jsou obklopeny maticí programovatelných propojení a jádro je obklopeno programovatelnými I / O buňkami.

FPGA se obvykle skládá z konfigurovatelných logických bloků, konfigurovatelných I / O bloků, programovatelných propojení, hodinových obvodů, ALU, paměti, dekodérů.

Viděli jsme různé dostupné typy ASIC. Nyní pochopíme, kdy jsou všechna tato přizpůsobení a propojení prováděna během výroby.

Návrhový tok integrovaného obvodu specifického pro aplikaci (ASIC)

Návrh ASIC se provádí krok za krokem. Toto pořadí kroků je známé jako ASIC design Tok. Kroky návrhového toku jsou uvedeny v následujícím vývojovém diagramu.

Návrhový tok ASIC

Návrhová položka: V tomto kroku je mikroarchitektura návrhu implementována pomocí jazyků popisu hardwaru, jako jsou VHDL, Verilog a System Verilog.

Logická syntéza: V tomto kroku se pomocí HDL připraví netlist logických buněk, které se mají použít, typy propojení a všechny ostatní části potřebné pro aplikaci.

Rozdělení systému: V tomto kroku rozdělíme kostku velké velikosti na kousky velikosti ASIC.

Simulace před rozvržením: V tomto kroku se provede simulační test ke kontrole, zda návrh obsahuje nějaké chyby.

Plánování podlaží: V tomto kroku jsou na čipu uspořádány bloky netlistu.

Umístění: V tomto kroku je rozhodnuto o umístění buněk uvnitř bloku.

Směrování: V tomto kroku se nakreslí spojení mezi bloky a buňkami. Extrakce: V tomto kroku určíme elektrické vlastnosti, jako je hodnota odporu a hodnota kapacity propojení.

Simulace po rozložení: Před odesláním modelu pro výrobu se tato simulace provede, aby se zkontrolovalo, zda systém funguje správně, spolu se zátěží propojení.

Příklady ASIC

Po seznámení s různými charakteristikami ASIC si nyní ukážeme několik příkladů ASIC.

Standardní buňkový ASIC: LCB 300k, 500k od LSI Logic Company, SIG1, 2, 3 rodiny od ABB Hafo Inc., GCS90K od GCS Plessey.

Gate Array produkty: AUA20K od Harris Semiconductor, SCX6Bxx od National Semiconductors, rodiny TGC / TEC od Texas Instruments.

Produkty PLD: Rodina pokročilých mikro zařízení PAL, rodina GAL od společnosti Philips Semiconductors, XC7300 a EPLD od společnosti XILINX.

Produkty FPGA: Řady XC2000, XC3000, XC4000, XC5000 od společnosti XILINX, pASIC1 společnosti QuickLogic, MAX5000 od společnosti Altera.

Aplikace ASIC

Jedinečnost ASIC způsobila revoluci ve způsobu výroby elektroniky. Ty zmenšily velikost matrice a zvýšily hustotu logické brány na čip. ASIC jsou obvykle preferovány pro aplikace na vysoké úrovni. Čip ASIC se používá jako IP jádra pro satelity, výrobu ROM, Mikrokontrolér a různé typy aplikací v lékařském a výzkumném sektoru. Jednou z trendových aplikací ASIC je BITCOIN MINER.

Bitcoin Miner

Těžba kryptoměny vyžaduje větší výkon a vysokorychlostní hardware. Univerzální CPU nemůže poskytnout tak vyšší výpočetní kapacitu při vysoké rychlosti. Těžař bitcoinů ASIC jsou čipy zabudované do speciálně navržených základních desek a zásoby energie , zkonstruované do jedné jednotky. Jedná se o záměrně navržený hardware až po úroveň čipů pro těžbu bitcoinů. Tyto jednotky mohou provádět algoritmus pouze jedné kryptoměny. Pravděpodobně pro jiný typ kryptoměny potřebujeme jiného horníka.

Výhody a nevýhody ASIC

The výhody ASIC zahrnout následující.

- Díky malé velikosti ASIC je vysokou volbou pro sofistikované větší systémy.

- Vzhledem k velkému počtu obvodů postavených na jediném čipu to způsobuje vysokorychlostní aplikace.

- ASIC má nízkou spotřebu energie.

- Jelikož se jedná o systém na čipu, obvody jsou přítomny vedle sebe. Pro připojení různých obvodů je tedy zapotřebí velmi minimální směrování.

- ASIC nemá žádné problémy s časováním a postprodukční konfiguraci.

The nevýhody ASIC zahrnout následující.

- Jelikož se jedná o přizpůsobené čipy, poskytují programování nízkou flexibilitu.

- Protože tyto čipy musí být navrženy od kořenové úrovně, mají vysoké náklady na jednotku.

- ASIC mají větší čas na tržní marži.

ASIC vs FPGA

Rozdíl mezi ASIC a FPGA zahrnuje následující.

ASIC | FPGA |

| Nelze přeprogramovat | Přeprogramovatelné |

| Preferováno pro velkoobjemové produkce | Preferováno pro nízkoobjemové produkce |

| Jedná se o konkrétní aplikaci | Používá se jako prototypy systému |

| Energeticky efektivní vyžaduje méně energie | Méně energeticky efektivní vyžaduje více energie |

| Jedná se o trvalé obvody, které nelze čas od času upgradovat. | Velmi vhodné pro aplikace, kde je třeba čas od času upgradovat obvod, jako jsou čipy mobilních telefonů, základnové stanice atd |

Jedná se tedy o přehled Integrovaný obvod specifický pro aplikaci . Vynález ASIC způsobil obrovskou změnu ve způsobu používání elektroniky. ASIC používáme v našem každodenním životě v podobě různých aplikací. Na jaké aplikace ASIC jste narazili? S jakým typem ASIC jste pracovali?