The kombinační obvody nepoužívejte žádný druh paměti. Proto dřívější poloha vstupu nezahrnuje žádný výsledek za současné situace obvodu. I když sekvenční obvod obsahuje paměť, výstup následně závisí na vstupu, což znamená, že výstup se může na základě vstupu měnit. Fungování těchto obvodů lze provést využitím předchozího vstupu obvodu, CLK, paměti a výstupu. Tento článek pojednává o přehledu flip flopu master-slave. Ale než se dozvíte o tomto klopném obvodu, musíte vědět o základech žabky jako flip flop SR a flip flop JK.

Co je to Master-Slave Flip Flop?

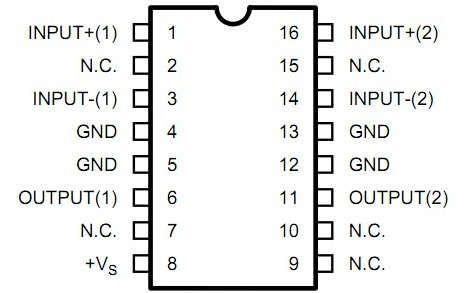

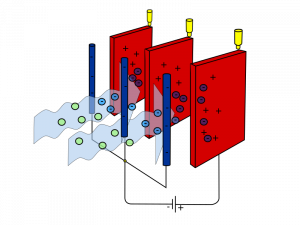

V zásadě lze tento typ klopného obvodu navrhnout se dvěma JK FF zapojením do série. Jeden z těchto FF, jeden FF pracuje jako master a další FF pracuje jako slave. Spojení těchto FF lze provést takto, výstup hlavního FF lze připojit ke vstupům podřízeného FF. Zde lze podřízené výstupy FF připojit ke vstupům hlavního FF.

U tohoto typu FF střídač se také používá jako doplněk ke dvěma FF. Připojení invertoru lze provést tak, že tam, kde lze invertovaný pulz CLK připojit k podřízenému FF. Jinými slovy, pokud je CLK puls 0 pro hlavní FF, pak CLK puls bude 1 pro podřízený FF. Podobně, když je CLK puls 1 pro hlavní FF, pak CLK puls bude 0 pro podřízený FF.

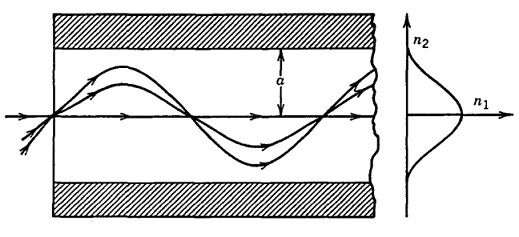

master-slave-flip-flop-obvod

Master-Slave FF pracuje

Kdykoli CLK pulz stoupne na vysokou hodnotu, což znamená 1, pak lze slave oddělit, vstupy jako J & K mohou změnit stav systému.

Podřízený FF může být odpojen, dokud puls CLK neklesne na nízkou hodnotu, což znamená 0. Kdykoli se pulz CLK vrátí zpět do nízkého stavu, lze data přenášet z nadřazeného FF do podřízeného FF a nakonec o / p lze získat.

Nejprve bude hlavní FF spuštěn na kladné úrovni, zatímco podřízený FF bude spuštěn na záporné úrovni. Z tohoto důvodu reaguje hlavní FF jako první.

Pokud J = 0 & K = 1, pak výstup hlavního FF ‚Q 'přejde na vstup K podřízeného FF & CLK vynutí podřízený FF na RST (reset), proto podřízený FF zkopíruje hlavní FF.

Pokud J = 1 & K = 0, potom hlavní FF „Q“ přejde na vstup J podřízeného FF a záporný přechod CLK nastaví podřízený FF a zkopíruje hlavní.

Pokud J = 1 & K = 1, pak přepíná přes pozitivní přechod CLK, a proto otrok přepíná přes negativní přechod CLK.

Pokud jsou oba J & K 0, pak FF může být imobilizován a Q zůstává nepohyblivý.

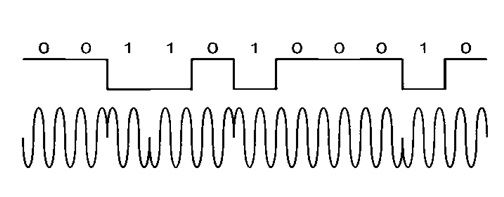

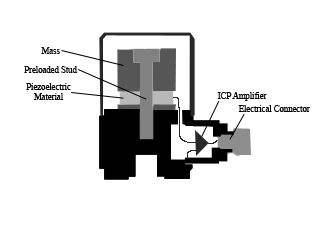

Časový diagram

- Jsou-li oba CLK pulsy & o / p na masteru vysoké, pak zůstávají vysoké, dokud CLK je nízká kvůli stavu je uložen.

- V současné době se o / p masteru mění na nízkou úroveň, protože puls CLK se opět mění na vysokou a zůstává nízký, dokud se CLK opět nezmění na vysokou.

- Přepínání proto probíhá u cyklu CLK.

timing-diagram-of-a-master-slave-FF

- Kdykoli je pulz CLK 1, je nastaven master, nikoli však slave, proto slave o / p zůstává „0“, dokud CLK nezůstane 1.

- Když je CLK nízká, pak se podřízená jednotka změní na funkční a zůstane „1“, dokud se CLK opět nezmění na „0“.

- Přepínání probíhá během celé procedury, zatímco se o / p mění jednou v cyklu.

- Díky tomu je tento klopný obvod jako synchronní zařízení, protože předává pouze data s časováním signálu CLK.

Jedná se tedy o Master-Slave Žabky . Z výše uvedených informací nakonec můžeme dojít k závěru, že tento FF může být sestaven se dvěma FF, a to master a slave. Když jeden FF funguje jako hlavní obvod, aktivuje se přes náběžnou hranu impulzu CLK. Podobně, když další FF funguje jako podřízený obvod, pak se aktivuje přes sestupnou hranu impulzu CLK.