Zvýšení rychlosti provádění programu následně zvýší rychlost procesor. Existuje mnoho způsobů, jak zvýšit rychlost provádění, jak implementací hardwaru, tak softwarovou architekturou. Bylo zjištěno, že současným prováděním pokynů lze zkrátit čas potřebný k provedení. Koncept paralelismu v programování bylo navrženo. Podle toho lze za hodinový cyklus provést více než jednu instrukci. Tento koncept může být praktikován programátorem pomocí různých technik, jako je Pipelining, Multiple execution units, and multiple cores . Ze všech těchto paralelních metod se nejčastěji praktikuje pipeline. Jak tedy lze provést instrukci v metodě pipelining? Jak zvyšuje rychlost provádění?

Co je to Pipelining?

Abychom pochopili koncept pipeline, podívejme se na kořenovou úroveň provádění programu. Instrukce je nejmenší prováděcí paket programu. Každá instrukce obsahuje jednu nebo více operací. Jednoduché skalární procesory provádějí jednu nebo více instrukcí za taktovací cyklus, přičemž každá instrukce obsahuje pouze jednu operaci. Pokyny jsou prováděny jako sled fází, aby se dosáhlo očekávaných výsledků. Tato sekvence je uvedena níže

Sekvence provádění pokynů

- IF: Načte instrukci do registru instrukcí.

- ID: Instruction Decode, dekóduje instrukci pro operační kód.

- AG: Generátor adres, generuje adresu.

- DF: Data Fetch, načte operandy do datového registru.

- EX: Provedení, provede zadanou operaci.

- WB: Write back, write write the result to registrace.

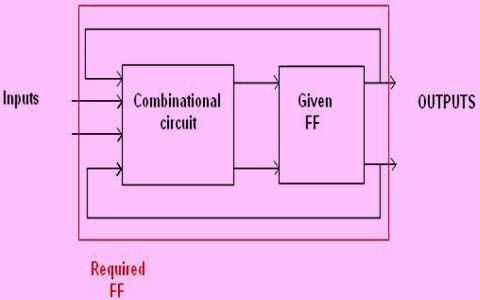

Ne všechny pokyny vyžadují všechny výše uvedené kroky, ale většina ano. Tyto kroky používají různé hardwarové funkce. V pipeline jsou tyto různé fáze prováděny souběžně. V pipeline jsou tyto fáze považovány za nezávislé mezi různými operacemi a mohou se překrývat. Lze tedy provádět více operací současně, přičemž každá operace je ve své vlastní nezávislé fázi.

Pokyny Pipelining

Podívejme se, jak jsou pokyny zpracovávány v pipeline. To lze snadno pochopit podle níže uvedeného diagramu.

Pokyny Pipelining

Předpokládejme, že pokyny jsou nezávislé. V jednoduchém pipeline procesoru je v daném čase v každé fázi pouze jedna operace. Počáteční fáze je fáze IF. Takže při prvním hodinovém cyklu je načtena jedna operace. Když dorazí další hodinový puls, první operace přejde do fáze ID a fáze IF zůstane prázdná. Nyní je tato prázdná fáze přidělena další operaci. Takže během druhého hodinového pulzu je první operace ve fázi ID a druhá operace je ve fázi IF.

Pro třetí cyklus bude první operace ve fázi AG, druhá operace bude ve fázi ID a třetí operace bude ve fázi IF. Tímto způsobem jsou instrukce prováděny souběžně a po šesti cyklech bude procesor vydávat kompletně provedenou instrukci za taktovací cyklus.

Prováděla se tato instrukce postupně, nejprve musí první instrukce projít všemi fázemi, potom by byla načtena další instrukce? Pro provedení každé instrukce by tedy procesor vyžadoval šest hodinových cyklů. Ale v zřetězeném procesoru, protože provádění instrukcí probíhá souběžně, pouze počáteční instrukce vyžaduje šest cyklů a všechny zbývající instrukce jsou prováděny jako jeden na každý cyklus, čímž se snižuje doba provádění a zvyšuje rychlost procesoru.

Pipelining Architecture

Paralelismu lze dosáhnout pomocí hardwarových, kompilátorových a softwarových technik. Využít koncept pipeline v počítačová architektura mnoho procesorových jednotek je vzájemně propojeno a funguje souběžně. V architektuře zřetězeného procesoru existují oddělené jednotky zpracování poskytované pro celá čísla a instrukce s plovoucí desetinnou čárkou. Zatímco v sekvenční architektuře je k dispozici jedna funkční jednotka.

Pipelined Processor Unit

Ve statickém pipeline by procesor měl předat instrukci všemi fázemi potrubí bez ohledu na požadavek instrukce. V dynamickém procesoru potrubí může instrukce obejít fáze v závislosti na svém požadavku, ale musí se pohybovat v postupném pořadí. Ve složitém procesoru s dynamickým potrubím může instrukce obejít fáze a také zvolit fáze mimo pořadí.

Pipeline v procesorech RISC

Nejpopulárnější RISC architektura Procesor ARM sleduje 3stupňové a 5stupňové pipeline. Ve třístupňovém pipeline jsou fáze: Fetch, Decode a Execute. Toto pipeline má latenci 3 cyklů, protože individuální instrukce trvá 3 hodinové cykly.

ARM 3 fáze Pipelining

Pro správnou implementaci pipeline by měla být také upgradována architektura hardwaru. Hardware pro třístupňové pipeline zahrnuje registrační banku, ALU, barel shifter, generátor adres, přírůstek, instrukční dekodér a datové registry.

ARM 3 Stage Pipelining Datapath

V 5 fázích pipeline jsou fáze: Fetch, Decode, Execute, Buffer / data a Write back.

Nebezpečí potrubí

V typickém počítačovém programu kromě jednoduchých instrukcí existují instrukce větvení, přerušení provozu, čtení a zápis instrukcí. Pipelining není vhodný pro všechny druhy pokynů. Když jsou některé pokyny prováděny v pipeline, mohou zastavit potrubí nebo jej úplně propláchnout. Tento typ problémů způsobených během pipeline se nazývá Pipelining Hazards.

Ve většině počítačových programů je výsledek jedné instrukce používán jako operand druhou instrukcí. Když jsou takové instrukce prováděny v pipeline, dojde k rozbití, protože výsledek první instrukce není k dispozici, když instrukce dvě začne sbírat operandy. Instrukce dva se tedy musí zastavit, dokud nebude provedena instrukce jedna a nebude vygenerován výsledek. Tento typ nebezpečí se nazývá Přečtení - riziko přepsání po zápisu.

Přečíst po zápisu Nebezpečí pipeliningu

Provádění pokynů k odbočkám také způsobuje nebezpečí zřetězení. Pokyny pobočky při provádění v potrubí ovlivní fáze načítání dalších pokynů.

Pipelined Branch Behavior

Výhody potrubí

- Zvyšuje se propustnost instrukcí.

- Zvýšení počtu fází potrubí zvyšuje počet současně prováděných instrukcí.

- Při použití potrubí lze navrhnout rychlejší ALU.

- Pipeline CPU pracuje na vyšších taktovacích frekvencích než RAM.

- Pipelining zvyšuje celkový výkon CPU.

Nevýhody potrubí

- Návrh pipeline procesoru je složitý.

- Zvyšuje se latence instrukcí u zřetězených procesorů.

- Je obtížné předvídat propustnost zřetězeného procesoru.

- Čím delší je potrubí, tím horší je problém rizika pro pokyny odbočky.

Pipelining přináší výhody všem pokynům, které se řídí podobnou posloupností kroků při provádění. Procesory, které mají složité instrukce, kde se každá instrukce chová odlišně od druhé, je obtížné pipeline. Procesory mají rozumné nástroje se 3 nebo 5 fázemi potrubí, protože se zvyšující se hloubkou potrubí se zvyšují rizika s ním spojená. Pojmenovat některé zřetězené procesory s jejich fází potrubí?

![Ovládání světel, ventilátoru pomocí dálkového ovládání TV [Plný obvodový diagram]](https://electronics.jf-parede.pt/img/3-phase-power/43/control-lights-fan-using-tv-remote-full-circuit-diagram-1.jpg)