V tomto příspěvku se naučíme, jak vytvořit logická hradla NOT, AND, NAND, OR a NOR pomocí diskrétních tranzistorů. Hlavní výhodou použití tranzistorových logických hradel je, že mohou pracovat i s napětím 1,5 V.

V některých elektronických aplikacích může být dostupné napětí nedostatečné pro napájení TTL nebo dokonce CMOS IC. To platí zejména pro gadgety, které fungují na baterie. Není pochyb o tom, že vždy máte možnost 3V logického integrovaného obvodu. Ty však nejsou pro nadšence nebo experimentátory vždy snadno dostupné a nepracují pod jejich definovanými napěťovými specifikacemi (obecně pod 2,5 V DC).

Kromě toho může být v bateriově napájené aplikaci místo pouze pro jednu 1,5voltovou baterii. No, tak co budeš dělat? Obvykle IC logická hradla by mohly být nahrazeny tranzistorovými logickými hradly. Pro každé konkrétní logické hradlo je obecně vyžadováno pouze několik tranzistorů a pro typickou logiku invertorového obvodu NOT hradlový pouze jeden tranzistor.

FET versus bipolární tranzistor

Tranzistory s efektem pole (FET) vs bipolární tranzistory : která je lepší varianta pro nízkonapěťové logické obvody? Jedna skvělá vlastnost FAKTA je, že jejich 'zapnutí' odpor je neuvěřitelně nízký. Navíc potřebují velmi nízký spínací proud brány.

V extrémně nízkonapěťových aplikacích však mají jedno omezení. Obvykle je limit napětí brány jeden volt nebo tak. Kromě toho se dostupné napětí může snížit pod optimální pracovní rozsah FET, pokud je k bráně připojen proud omezující nebo stahovací odpor.

Naopak bipolární spínací tranzistory mají výhodu v extrémně nízkonapěťových aplikacích s jednou baterií, protože k sepnutí potřebují pouze 0,6 až 0,7 voltů.

Kromě toho je většina běžných FET, které se běžně prodávají v bublinkovém balení v nejbližším obchodě s elektronikou, často dražší než bipolární tranzistory. Také hromadný balík bipolárních tranzistorů by se mohl obecně zakoupit za cenu páru FET.

Manipulace s FET vyžaduje podstatně větší péči než manipulace s bipolárním tranzistorem. Elektrostatické a obecné experimentální zneužití činí FET obzvláště náchylné k poškození. Spálené komponenty mohou zničit příjemný, kreativní večer experimentování nebo inovací, nesmíme zapomenout na emocionální bolest při ladění.

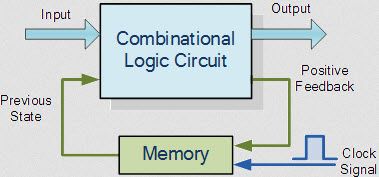

Základy spínacích tranzistorů

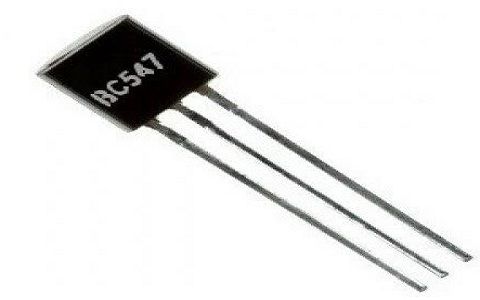

Příklady logických obvodů vysvětlené v tomto článku využívají bipolární tranzistory NPN, protože jsou cenově dostupné a nevyžadují zvláštní manipulaci. Aby nedošlo k poškození zařízení nebo jeho částí, je třeba před připojením vašeho obvodu provést vhodná bezpečnostní opatření.

I když jsou naše obvody převážně zaměřeny na bipolární tranzistory (BJT), mohly být stejně dobře konstruovány pomocí technologie FET.

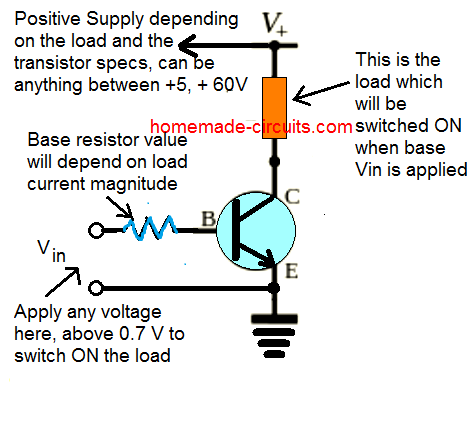

Základní spínací obvod je jednoduchá tranzistorová aplikace, která je jednou z nejjednodušších konstrukcí.

Vytvoření brány NOT s jedním tranzistorem

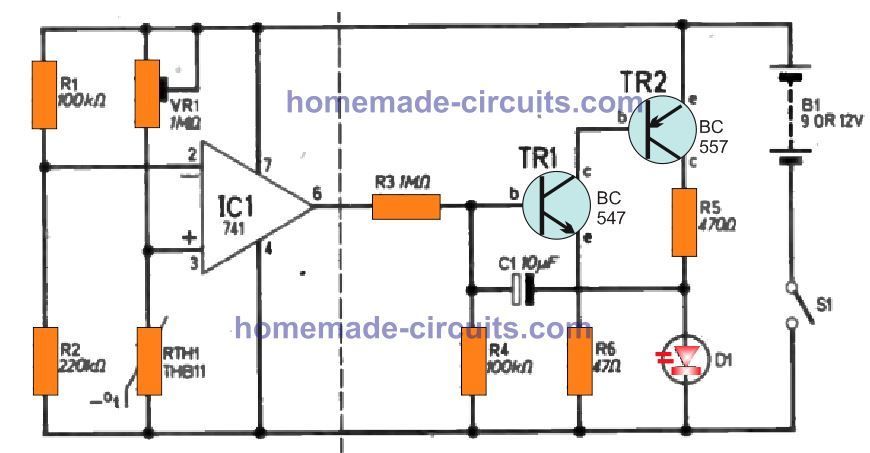

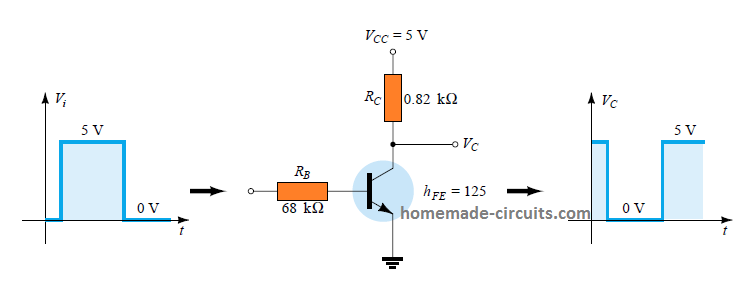

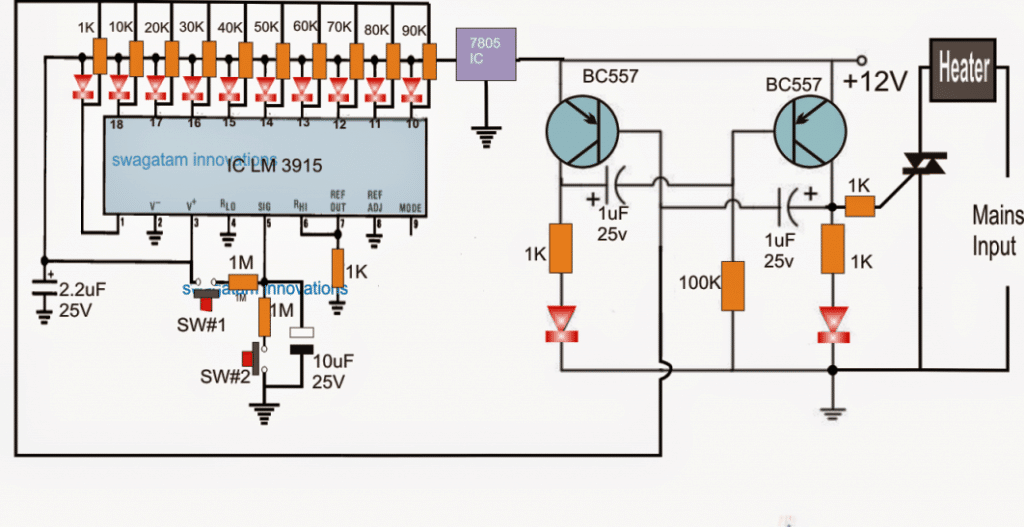

Schéma tranzistorového spínače je znázorněno na obrázku 1. V závislosti na tom, jak je implementován v konkrétní aplikaci, může být spínač považován buď za udržovaný na nízké úrovni, nebo normálně otevřený.

Jednoduchý logický hradlový invertorový hradlo NOT může být vytvořen přímočarým spínacím obvodem znázorněným na obr. 1 (kde bod A je vstup). Hradlo NOT funguje tak, že pokud není na bázi tranzistoru (bod A; Q1) poskytnuto žádné stejnosměrné předpětí, zůstane tranzistor vypnutý, což vede k vysoké nebo logické 1 (rovné úrovni V+) na výstupu ( bod B).

Tranzistor se však aktivuje, když je do báze Q1 poskytnuto správné předpětí, čímž se výstup obvodu stlačí na nízkou úroveň nebo na logickou 0 (téměř rovno nulovému potenciálu). Tranzistor, označený Q1, je bipolární tranzistor pro všeobecné použití nebo BC547, který se obvykle používá v nízkopříkonových spínacích a zesilovacích aplikacích.

Jakýkoli tranzistor, který je mu ekvivalentní (např. 2N2222, 2N4401 atd.), by fungoval. Hodnoty R1 a R2 byly zvoleny tak, aby bylo dosaženo kompromisu mezi nízkým odběrem proudu a kompatibilitou. Ve všech provedeních jsou všechny rezistory 1/4 wattu, 5% jednotek.

Napájecí napětí je nastavitelné mezi 1,4 a 6 V DC. Všimněte si, že obvod může fungovat jako vyrovnávací paměť, když jsou zatěžovací odpor a výstupní připojení posunuty k emitoru tranzistoru.

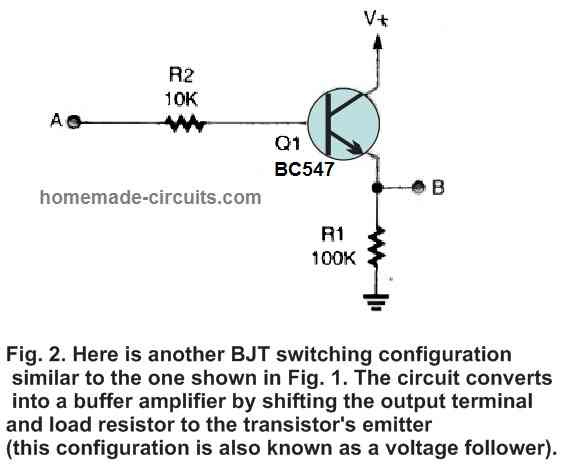

Vytvoření vyrovnávací brány pomocí jediného BC547 BJT

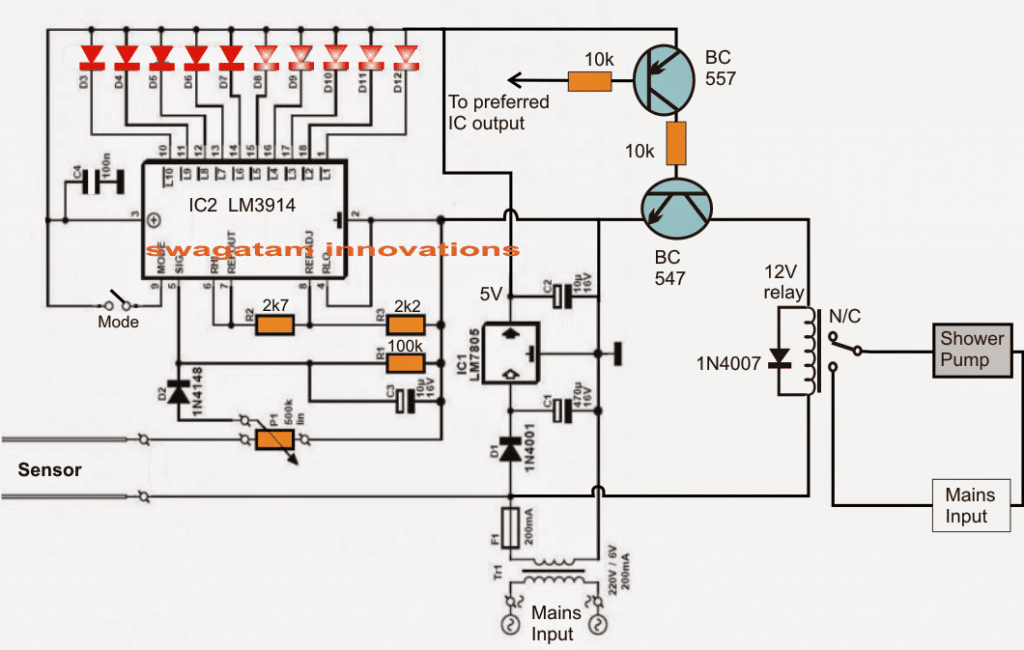

Napěťový sledovač neboli vyrovnávací zesilovač je typem konfigurace logického spínání identického s konfigurací znázorněnou na obrázku 2. Je třeba poznamenat, že zatěžovací odpor a výstupní svorka byly v tomto obvodu posunuty z kolektoru tranzistoru na jeho emitor, což je hlavní rozdíl mezi tímto provedením a návrhem znázorněným na obr. 1.

Fungování tranzistoru lze také 'převrátit' přemístěním zatěžovacího odporu a výstupní svorky na druhý konec BJT.

Jinými slovy, když není zajištěno žádné předpětí na vstupu obvodu, výstup obvodu zůstává nízký; když je však na vstup obvodu přivedeno předpětí přiměřeného napětí, výstup obvodu se změní na vysoký. (To je přesný opak toho, co se děje v předchozím okruhu.)

Navrhování dvouvstupových logických hradel pomocí tranzistorů

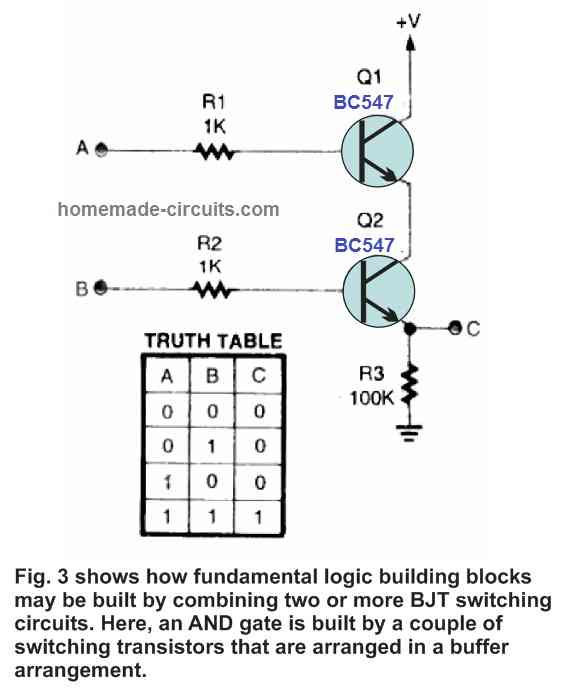

AND Gate pomocí dvou tranzistorů

Obrázek 3 ilustruje, jak lze vytvořit základní dvouvstupové hradlo AND pomocí dvojice vyrovnávacích pamětí spolu s pravdivostní tabulkou pro toto hradlo. Pravdivostní tabulka ukazuje, jaké by byly výstupní výsledky pro každou odlišnou sadu vstupů. Body A a B se používají jako vstupy obvodu a bod C slouží jako výstup obvodu.

Z pravdivostní tabulky je důležité poznamenat, že pouze jedna sada vstupních parametrů má za následek logický-vysoký výstupní signál, zatímco všechny ostatní vstupní kombinace vedou k logickému-nízkému výstupu. Výstup hradla AND na obrázku 3 zůstává mírně pod V+, jakmile se změní na vysoký.

To se děje kvůli poklesu napětí mezi dvěma tranzistory (Q1 a Q2).

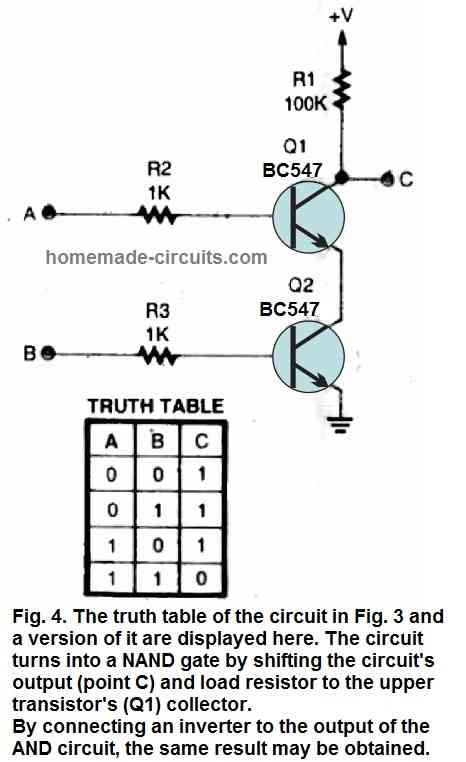

Brána NAND pomocí dvou tranzistorů

Další varianta obvodu na obrázku 3 a související pravdivostní tabulka jsou uvedeny na obrázku 4. Obvod se změní na hradlo NAND posunutím výstupu (bod C) a výstupního odporu do kolektoru horního tranzistoru (Q1).

Protože oba Q1 a Q2 musí být zapnuty, aby se přitáhla spodní strana R1 k zemi, ztráta napětí na výstupu C je nevýznamná.

Pokud tranzistorová AND nebo tranzistorová hradla NAND potřebují více než dva vstupy, mohlo by být v ukázaných provedeních zapojeno více tranzistorů, aby poskytly tři, čtyři atd. vstupní AND nebo NAND hradla.

Aby se však kompenzovaly napěťové ztráty jednotlivých tranzistorů, mělo by se odpovídajícím způsobem zvýšit V+.

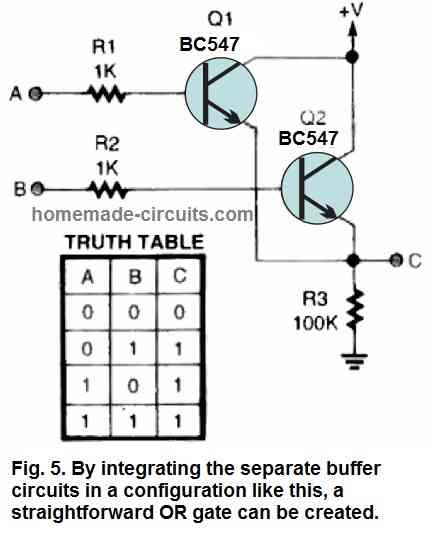

NEBO Brána pomocí dvou tranzistorů

Další forma logického obvodu se dvěma vstupy je vidět na obrázku 5 spolu s pravdivostní tabulkou obvodu OR-gate.

Výstup obvodu je vysoký, když je buď vstup A nebo vstup B posunut vysoko, ale kvůli kaskádovým tranzistorům je pokles napětí přes 0,5 voltu. Zobrazená čísla opět ukazují, že je zde dostatek napětí a proudu pro ovládání následujícího hradla tranzistoru.

NOR Gate pomocí dvou tranzistorů

Obrázek 6 znázorňuje další hradlo na našem seznamu, dvouvstupové hradlo NOR, spolu s jeho pravdivostní tabulkou. Podobně jako brány AND a NAND na sebe reagují, obvody OR a NOR dělají totéž.

Každé ze zobrazených hradel je schopné dodávat dostatek pohonu pro aktivaci alespoň jednoho nebo více sousedních hradel tranzistoru.

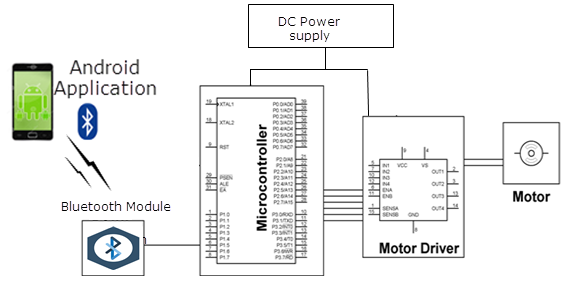

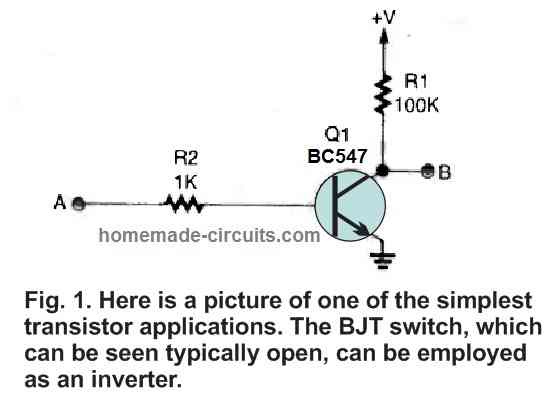

Aplikace tranzistorových logických hradel

Co děláte s výše vysvětlenými digitálními obvody, které nyní vlastníte? Cokoli, čeho byste mohli dosáhnout s konvenčními hradly TTL nebo CMOS, ale bez obav z omezení napájecího napětí. Zde je několik aplikací tranzistorových logických hradel v akci.

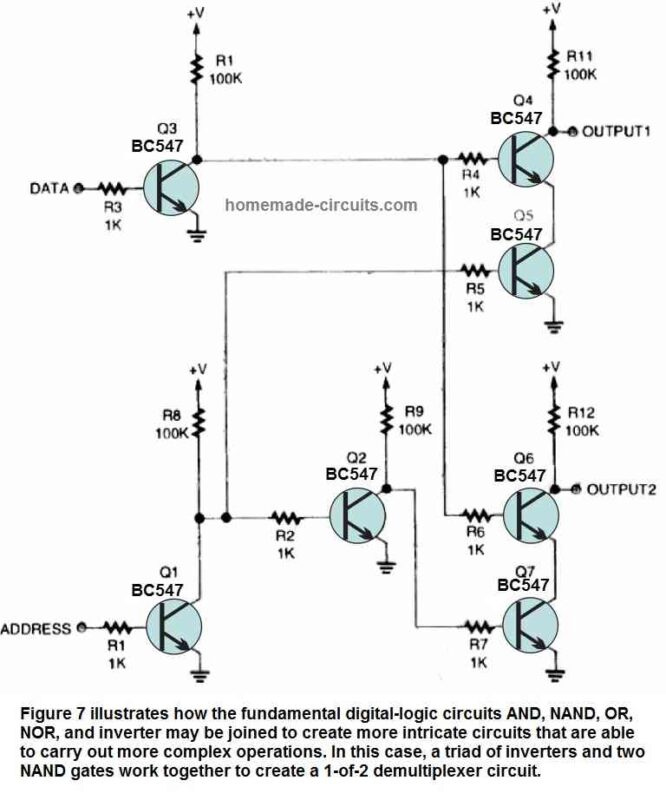

Demultiplexní obvod

Demultiplexor 1 ze 2 se třemi hradly NOT a dvěma obvody NAND je vidět na obrázku 7. Příslušný výstup je vybrán pomocí jednobitového „adresového vstupu“, který může být buď OUTPUT1 nebo OUTPUT2, přičemž jsou aplikovány řídicí informace. do obvodu pomocí vstupu DATA.

Obvod pracuje nejúčinněji, když je datová rychlost udržována pod 10 kHz. Funkce obvodu je přímočará. Vstup DATA je dodáván s požadovaným signálem, který zapne Q3 a invertuje příchozí data na kolektoru Q3.

Výstup Q1 je buzen vysoko, pokud je vstup ADDRESS nízký (uzemněný nebo není poskytován žádný signál). Na kolektoru Q1 je vysoký výkon rozdělen do dvou cest. V první cestě je výstup Q1 přiveden do základny Q5 (jedné z nohou dvouvstupové brány NAND), čímž se zapne a tím se „aktivuje“ brána NAND složená z Q4 a Q5.

Ve druhé cestě je vysoký výstup Q1 současně dodáván do vstupu dalšího hradla NOT (Q2). Po dvojité inverzi se výstup Q2 sníží. Toto nízké napětí je napájeno základnou Q7 (jeden vývod druhého hradla NAND, tvořeného Q6 a Q7), čímž se obvod NAND vypíná.

Jakákoli informace nebo signál přivedený na vstup DATA za těchto okolností dorazí na OUTPUT1. Případně je situace opačná, pokud je na vstup ADDRESS dán vysoký signál. To znamená, že veškeré informace poskytnuté obvodu se zobrazí na VÝSTUPU2, protože hradlo NAND Q4/Q5 je deaktivováno a hradlo NAND Q6/Q7 je povoleno.

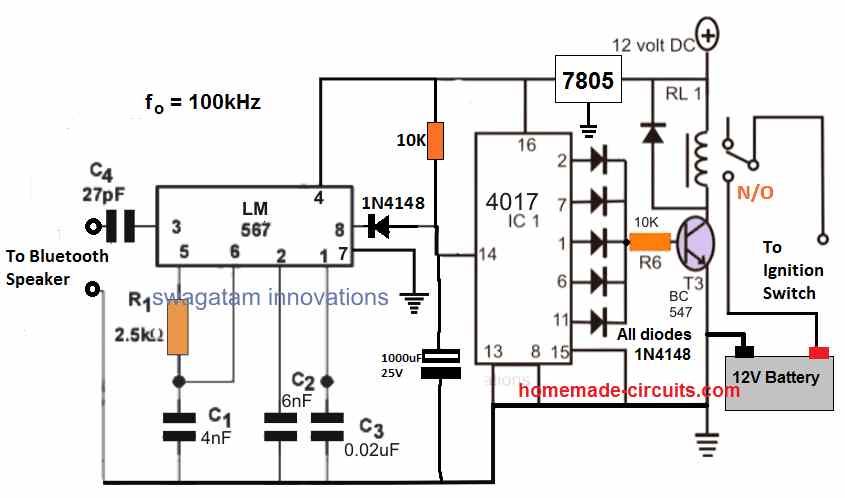

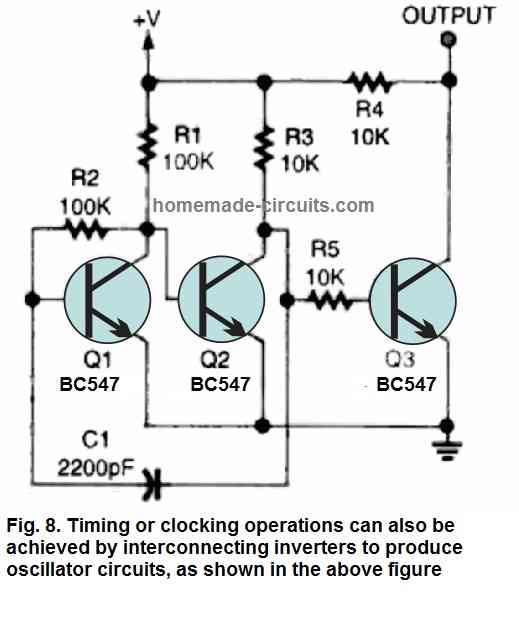

Oscilátorový obvod (generátor hodin)

Naše další aplikace logického hradla tranzistoru, znázorněná na obr. 8, je základní hodinový generátor (také známý jako oscilátor) vyrobený ze tří běžných hradlových invertorů NOT (jeden z nich je ovlivněn zpětnovazebním odporem R2, který jej vkládá do analogová oblast).

Pro kvadraturu výstupu je zahrnuta třetí brána NOT (Q3), která dodává doplněk k výstupu oscilátoru. Hodnotu C1 lze zvýšit nebo snížit, aby se změnila pracovní frekvence obvodu. Výstupní křivka má frekvenci přibližně 7 kHz s V+ při 1,5 V DC, s použitím uvedených hodnot komponent.

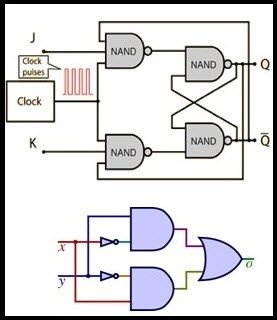

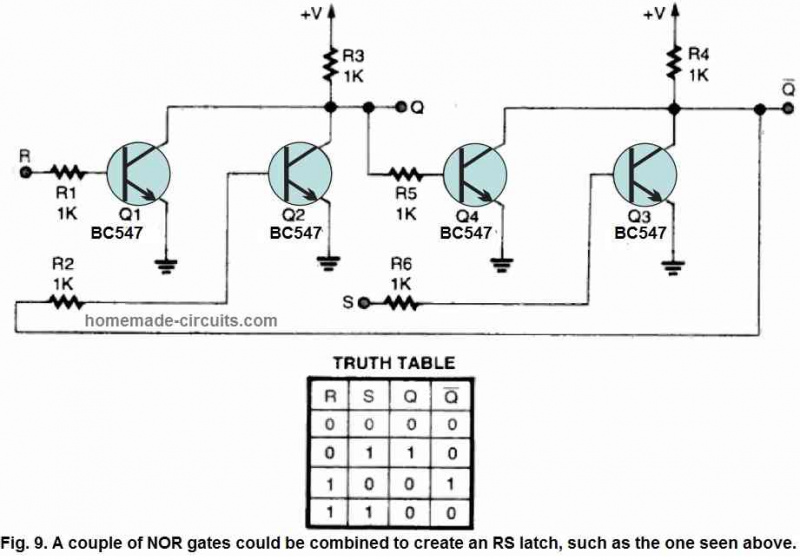

Obvod západky RS

Obr. 9 ukazuje náš konečný aplikační obvod, západku RS tvořenou dvěma hradly NOR. Pro zajištění zdravého výstupního pohonu na výstupech Q a Q jsou rezistory R3 a R4 nastaveny na 1 kΩ.

Pravdivostní tabulka západky RS je zobrazena vedle schématu. Toto je jen několik ilustrací několika důvěryhodných, nízkonapěťových, digitálních obvodů s logickým hradlem, které mohou být vytvořeny pomocí jednotlivých tranzistorů.

Obvody využívající tranzistorovou logiku potřebují příliš mnoho dílů

Mnoho problémů lze vyřešit pomocí všech těchto nízkonapěťových tranzistorových logických obvodů. Použití příliš velkého množství těchto tranzistorových hradel by však mohlo vést k novým problémům.

Počet tranzistorů a rezistorů může být poměrně velký, pokud aplikace, kterou vytváříte, obsahuje velké množství hradel, které zabírají cenný prostor.

Použití tranzistorových polí (mnoho tranzistorů uzavřených v plastu) a odporů SIP (Single Inline Package) namísto jednotlivých jednotek je jedním ze způsobů, jak tento problém vyřešit.

Výše uvedený přístup může ušetřit tunu místa na desce plošných spojů při zachování výkonu rovného výkonu jejich ekvivalentů v plné velikosti. Tranzistorová pole jsou nabízena v balení pro povrchovou montáž, 14pinový průchozí otvor a balení po čtyřech.

Pro většinu obvodů mohou být směšovací typy tranzistorů docela přijatelné.

Přesto je vhodné, aby experimentátor pracoval s jediným typem tranzistoru pro stavbu tranzistorových logických obvodů (to znamená, pokud vytvoříte sekci hradla pomocí BC547, zkuste použít stejný BJT pro výrobu ostatních zbývajících hradel).

Důvodem je, že různé varianty tranzistorů mohou mít poněkud odlišné vlastnosti, a proto se mohou chovat odlišně.

Například u některých tranzistorů může být limit zapnutí báze větší nebo menší než jiný, nebo může mít celkový proudový zisk o něco vyšší nebo nižší.

Na druhou stranu, náklady na nákup hromadné krabice jednoho typu tranzistoru by mohly být také nižší. Výkon vašich obvodů se zvýší, pokud jsou vaše logická hradla postavena pomocí odpovídajících tranzistorů, a projekt jako celek bude nakonec přínosnější.