Řídicí jednotka je hlavní složkou centrální procesorové jednotky (CPU) v počítačích, které mohou řídit operace během provádění programu procesor /počítač. Hlavní funkcí řídicí jednotky je načítání a provádění pokynů z paměti počítače. Přijímá vstupní instrukce / informace od uživatele a převádí je na řídicí signály , které jsou poté předány CPU k dalšímu provedení. Je zahrnuta jako součást architektury Von Neumann vyvinuté Johnem Neumannem. Je odpovědný za poskytování časovacích signálů a řídicích signálů a řídí provádění programu CPU. Je zahrnut jako vnitřní součást CPU v moderních počítačích. Tento článek popisuje úplné informace o řídicí jednotce.

Co je to řídicí jednotka?

Komponenta, která přijímá vstupní signál / informace / instrukci od uživatele a převádí se na řídicí signály pro provedení v CPU. Řídí a směruje hlavní paměť, aritmetickou a logickou jednotku (ALU), vstupní a výstupní zařízení a také odpovídá za pokyny, které jsou odesílány do CPU počítače. Načte pokyny z hlavní paměť procesoru a odeslán do registru instrukcí procesoru, který obsahuje obsah registru.

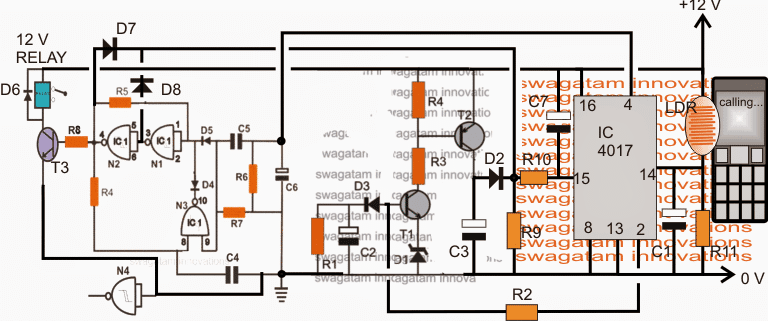

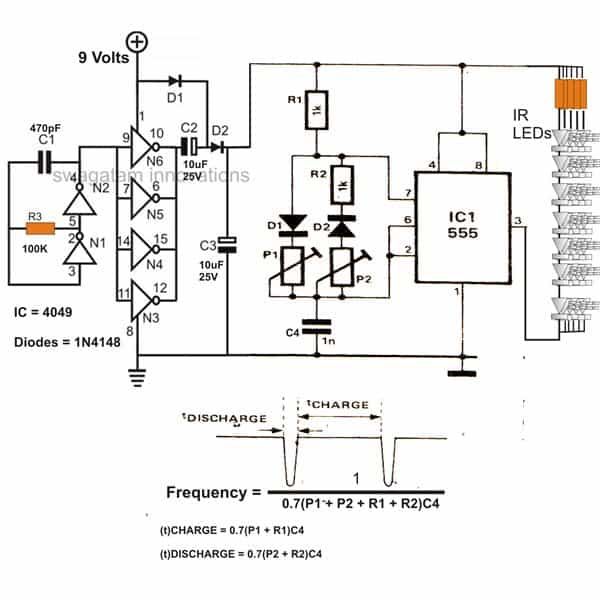

Blokové schéma řídicí jednotky

Řídicí jednotka převádí vstup na řídicí signály a poté je odesílána do procesoru a řídí provádění programu. Operace, které je třeba provést, jsou směrovány procesorem v počítači. Hlavně centrální procesorová jednotka (CPU) a Jednotka grafického zpracování (GPU) vyžadují jako vnitřní část řídicí jednotku. Blokové schéma řídicí jednotky je zobrazeno výše.

Součásti řídicí jednotky

Součásti této jednotky jsou instrukce registry , řídicí signály v CPU, řídicí signály do / ze sběrnice, řídicí sběrnice, vstupní příznaky a hodinové signály.

Součásti řídicí jednotky Hardwired jsou registr instrukcí (obsahuje operační kód a pole adresy), časovací jednotka, stav řízení generátor , matice generování řídícího signálu a dekodér instrukcí.

Komponenty mikroprogramované řídicí jednotky jsou další generátor adres, registr řídicích adres, řídicí paměť a registr řídicích dat.

Funkce

The funkce řídicí jednotky zahrnout následující.

- Usměrňuje tok datových sekvencí mezi procesorem a dalšími zařízeními.

- Může interpretovat pokyny a řídit tok dat v procesoru.

- Generuje sled řídicích signálů z přijatých instrukcí nebo příkazů z registru instrukcí.

- Má odpovědnost za řízení prováděcích jednotek, jako je ALU, datové vyrovnávací paměti a registry v CPU počítače.

- Má schopnost načítat, dekódovat, zpracovávat provádění a ukládat výsledky.

- Nemůže zpracovávat a ukládat data

- Pro přenos dat komunikuje se vstupními a výstupními zařízeními a ovládá všechny jednotky počítače.

Návrh řídicí jednotky

Návrh toho lze provést pomocí dvou typy řídicí jednotky které zahrnují následující.

- Hardwire založené

- Mikroprogramově založené (jednoúrovňové a dvouúrovňové)

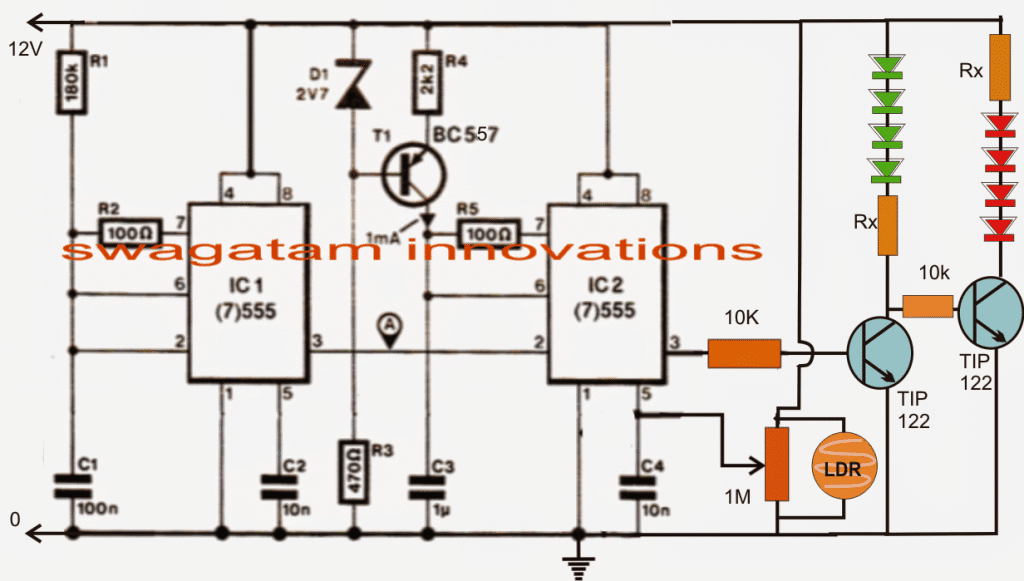

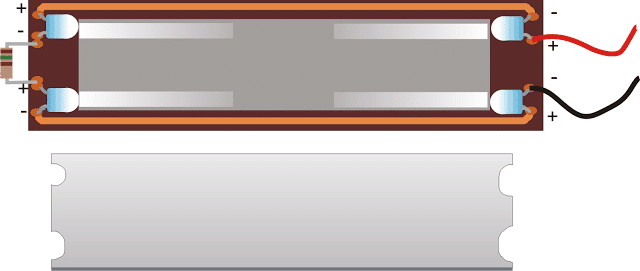

Pevně zapojená řídicí jednotka

Základní provedení pevně zapojené řídicí jednotky je uvedeno výše. U tohoto typu jsou řídicí signály generovány speciálním hardwarem logický obvod beze změny ve struktuře obvodu. V tomto případě nelze generovaný signál upravit pro provedení v procesoru.

Základní data operačního kódu (operační kód instrukce je odeslán do dekodéru instrukce pro dekódování. Instrukce dekodér je sada dekodérů pro dekódování různých typů dat v operačním kódu. To má za následek výstupní signály, které obsahují hodnoty aktivních signálů, které jsou dány jako vstup do generátoru matice pro generování řídicích signálů pro provádění programu procesorem počítače.

Hardwarová řídicí jednotka

Generátor matice poskytuje stavy řídicí jednotky a signálů vycházejících z procesoru (přerušovací signály). Matice je postavena jako programovatelné logické pole . Řídicí signály generované generátorem matice jsou uvedeny jako vstup do další matice generátoru a kombinují se s časovacími signály časovací jednotky, která obsahuje obdélníkové vzory.

Při načítání nové instrukce se řídicí jednotka změní v počáteční fázi provádění nové instrukce. Řídicí jednotka zůstává v počátečním nebo prvním stupni, dokud se nezmění časovací signály, vstupní signály a stav instrukce počítače. Změna stavu řídicí jednotky může být vyvolána, pokud dojde ke změně některého z generovaných signálů.

Když dojde k externímu signálu nebo přerušení, řídicí jednotka přejde do dalšího stavu a provede zpracování signálu přerušení. Příznaky a stavy se používají k výběru požadovaných stavů k provedení cyklu provádění instrukce.

V posledním stavu načte řídicí jednotka další instrukci a odešle výstup do čítače programu, poté do registru adres paměti, do vyrovnávací paměti a poté do registru instrukcí, aby instrukci přečetl. Nakonec, pokud je poslední instrukce (která je načtena řídicí jednotkou) koncovou instrukcí, přejde do provozního stavu procesoru a čeká, až uživatel nasměruje další program.

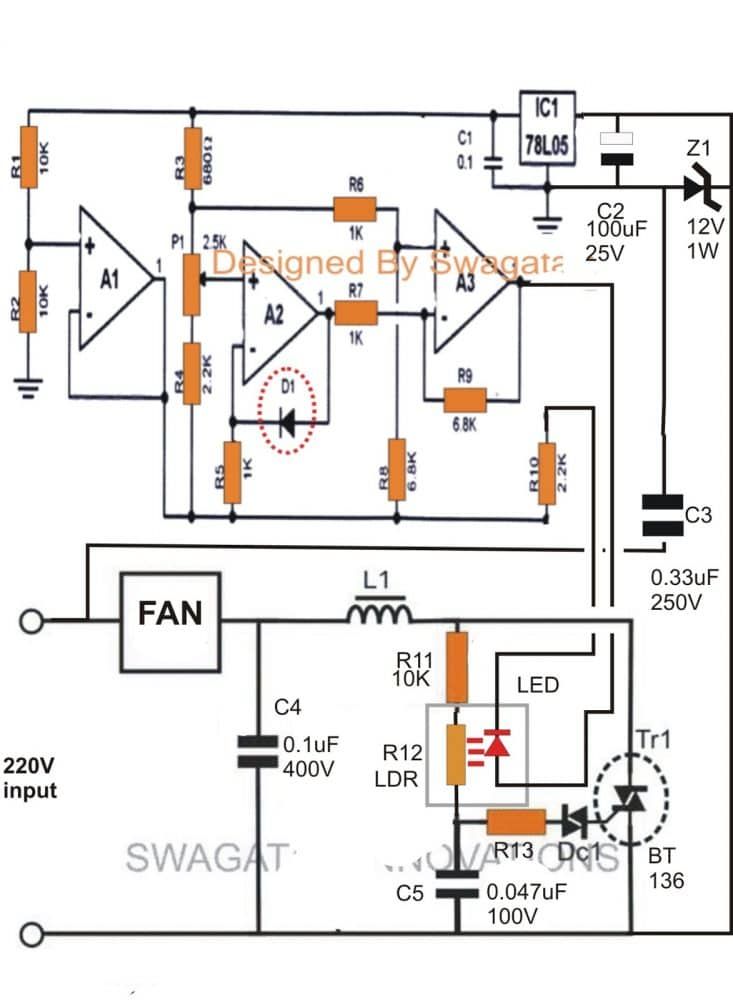

Mikroprogramovaná řídicí jednotka

V tomto typu se řídicí úložiště používá k ukládání řídicích signálů, které jsou kódovány během provádění programu. Řídicí signál není generován okamžitě a dekódován, protože mikroprogram ukládá pole adresy do řídicího úložiště. Celý proces je na jedné úrovni.

Mikrooperace se provádějí pro provádění mikroinstrukcí v programu. Blokové schéma mikroprogramované řídicí jednotky je zobrazeno výše. Z diagramu je adresa mikro-instrukce získána z registru adres řídicí paměti. Veškeré informace o řídicí jednotce jsou trvale uloženy v řídicí paměti zvané ROM.

Mikroprogramově založená řídicí jednotka

Mikro-instrukce z řídicí paměti je držena řídicím registrem. Vzhledem k tomu, že mikroinstrukce má formu řídicího slova (obsahuje binární řídicí hodnoty), je pro zpracování dat zapotřebí provést 1 nebo více mikrooperací.

Během provádění mikro-instrukcí další generátor adres vypočítal další adresu mikro-instrukce a poté odešle do registru řídicích adres pro přečtení další mikro-instrukce.

Sekvence mikrooperací mikroprogramu je prováděna dalším generátorem adres a funguje jako sekvencer mikroprogramů pro získání adresy sekvence, tj. Čtení z řídicí paměti.

Verilogový kód pro řídicí jednotku

Verilogový kód pro řídicí jednotku je uveden níže.

`zahrnout„ prj_definition.v “

modul CONTROL_UNIT (MEM_DATA, RF_DATA_W, RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2, RF_READ, RF_WRITE, ALU_OP1, ALU_OP2, ALU_OPRN, MEM_ADDR, MEM_READ, MEM_WRITE, RF_DATA_R1, RF_DATA_R1, RF_DATA_R_

// Výstupní signály

// Výstupy pro registr

výstup [`DATA_INDEX_LIMIT: 0] RF_DATA_W

výstup [`ADDRESS_INDEX_LIMIT: 0] RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2

výstup RF_READ, RF_WRITE

// Výstupy pro ALU

výstup [`DATA_INDEX_LIMIT: 0] ALU_OP1, ALU_OP2

výstup [`ALU_OPRN_INDEX_LIMIT: 0] ALU_OPRN

// Výstupy do paměti

výstup [`ADDRESS_INDEX_LIMIT: 0] MEM_ADDR

výstup MEM_READ, MEM_WRITE

// Vstupní signály

vstup [`DATA_INDEX_LIMIT: 0] RF_DATA_R1, RF_DATA_R2, ALU_RESULT

zadejte NULA, CLK, RST

// Signál Inout

inout [`DATA_INDEX_LIMIT: 0] MEM_DATA

// Státní sítě

drát [2: 0] proc_state

// uchovává hodnotu čítače programu, ukládá aktuální instrukci, registr ukazatele zásobníku

reg MEM_READ, MEM_WRITE

reg MEM_ADDR

reg ALU_OP1, ALU_OP2

reg ALU_OPRN

reg RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2

reg RF_DATA_W

reg [1: 0] state, next_state

PROC_SM state_machine (.STATE (proc_state) ,. CLK (CLK) ,. RST (RST))

vždy @ (posedge CLK)

začít

pokud (RST)

Stát<= RST

jiný

Stát<= next_state

konec

vždy @ (stát)

začít

MEM_READ = 1’b0 MEM_WRITE = 1’b0 MEM_ADDR = 1’b0

ALU_OP1 = 1’b0 ALU_OP2 = 1’b0 ALU_OPRN = 1’b0

RF_ADDR_R1 = 1’b0 RF_ADDR_R2 = 1’b0 RF_ADDR_W = 1’b0 RF_DATA_W = 1’b0

případ (stát)

`PROC_FETCH: začít

next_state = `PROC_DECODE

MEM_READ = 1’b1

RF_ADDR_R1 = 1’b0 RF_ADDR_R2 = 1’b0

RF_ADDR_W = 1’b1

konec

`PROC_DECODE: začít

next_state = `PROC_EXE

MEM_ADDR = 1’b1

ALU_OP1 = 1’b1 ALU_OP2 = 1’b1 ALU_OPRN = 1’b1

MEM_WRITE = 1’b1

RF_ADDR_R1 = 1’b1 RF_ADDR_R2 = 1’b1

konec

`PROC_EXE: začít

next_state = `PROC_MEM

ALU_OP1 = 1’b1 ALU_OP2 = 1’b1 ALU_OPRN = 1’b1

RF_ADDR_R1 = 1’b0

konec

`PROC_MEM: začít

next_state = `PROC_WB

MEM_READ = 1’b1 MEM_WRITE = 1’b0

konec

`PROC_WB: začít

next_state = `PROC_FETCH

MEM_READ = 1’b1 MEM_WRITE = 1’b0

konec

koncovka

konec

endmodul

modul PROC_SM (STAV, CLK, RST)

// seznam vstupů

vstup CLK, RST

// seznam výstupů

výstup [2: 0] STAV

// vstupní seznam

vstup CLK, RST

// výstupní seznam

výstup STATE

reg [2: 0] STAV

reg [1: 0] stát

reg [1: 0] next_state

reg PC_REG, INST_REG, SP_REF

`definujte PROC_FETCH 3’h0

`definujte PROC_DECODE 3’h1

`definujte PROC_EXE 3’h2

`definujte PROC_MEM 3’h3

`definujte PROC_WB 3’h4

// inicializace stavu

počáteční

začít

stav = 2’bxx

next_state = `PROC_FETCH

konec

// reset zpracování signálu

vždy @ (posedge RST)

začít

state = `PROC_FETCH

next_state = `PROC_FETCH

konec

vždy @ (posedge CLK)

začít

state = next_state

konec

vždy @ (stát)

začít

if (state === `PROC_FETCH)

začít

next_state = `PROC_DECODE

print_instruction (INST_REG)

konec

if (state === `PROC_DECODE)

začít

next_state = `PROC_EXE

konec

if (state === `PROC_EXE)

začít

next_state = `PROC_MEM

print_instruction (SP_REF)

konec

if (state === `PROC_MEM)

začít

next_state = `PROC_WB

konec

if (state === `PROC_WB)

začít

next_state = `PROC_FETCH

print_instruction (PC_REG)

konec

konec

úkol print_instruction

vstup [`DATA_INDEX_LIMIT: 0] inst

reg [5: 0] operační kód

reg [4: 0] rs

reg [4: 0] RT

reg [4: 0] rd

reg [4: 0] shamt reg [5: 0] funct reg [15: 0] okamžitá reg [25: 0] adresa

začít

// analyzovat instrukci

// Typ R.

{opcode, rs, rt, rd, shamt, funct} = inst

// Píši

{opcode, rs, rt, okamžitý} = inst

// Typ J.

{opcode, address} = inst

$ write („@% 6dns -> [0X% 08h]“, $ time, inst)

case (opcode) // R-Type

6'h00: start

případ (funkce)

6’h20: $ write („add r [% 02d], r [% 02d], r [% 02d]“, rs, rt, rd)

6’h22: $ write („sub r [% 02d], r [% 02d], r [% 02d]“, rs, rt, rd)

6’h2c: $ write („mul r [% 02d], r [% 02d], r [% 02d]“, rs, rt, rd)

6’h24: $ write („and r [% 02d], r [% 02d], r [% 02d]“, rs, rt, rd)

6’h25: $ write („nebo r [% 02d], r [% 02d], r [% 02d]“, rs, rt, rd)

6’h27: $ write („ani r [% 02d], r [% 02d], r [% 02d]“, rs, rt, rd)

6’h2a: $ write („slt r [% 02d], r [% 02d], r [% 02d]“, rs, rt, rd)

6’h00: $ write („sll r [% 02d],% 2d, r [% 02d]“, rs, shamt, rd)

6’h02: $ write („srl r [% 02d], 0X% 02h, r [% 02d]“, rs, shamt, rd)

6’h08: $ write („jr r [% 02d]“, rs)

výchozí: $ write (“”)

koncovka

konec

// Píši

6’h08: $ write („addi r [% 02d], r [% 02d], 0X% 04h“, rs, rt, okamžité)

6’h1d: $ write („muli r [% 02d], r [% 02d], 0X% 04h“, rs, rt, okamžité)

6’h0c: $ write („andi r [% 02d], r [% 02d], 0X% 04h“, rs, rt, okamžité)

6’h0d: $ write („ori r [% 02d], r [% 02d], 0X% 04h“, rs, rt, okamžité)

6’h0f: $ write („lui r [% 02d], 0X% 04h“, rt, okamžité)

6’h0a: $ write („slti r [% 02d], r [% 02d], 0X% 04h“, rs, rt, okamžité)

6’h04: $ write („beq r [% 02d], r [% 02d], 0X% 04h“, rs, rt, okamžité)

6’h05: $ write („bne r [% 02d], r [% 02d], 0X% 04h“, rs, rt, okamžité)

6’h23: $ write („lw r [% 02d], r [% 02d], 0X% 04h“, rs, rt, okamžité)

6’h2b: $ write („sw r [% 02d], r [% 02d], 0X% 04h“, rs, rt, okamžité)

// J-Type

6’h02: $ write („jmp 0X% 07h“, adresa)

6’h03: $ write („jal 0X% 07h“, adresa)

6’h1b: $ write („push“)

6’h1c: $ write („pop“)

výchozí: $ write (“”)

koncovka

$ write („ n“)

konec

endtask

koncový modul

Časté dotazy

1). Jaká je práce řídicí jednotky?

Úkolem řídicí jednotky je nasměrovat tok dat nebo instrukcí k provedení procesorem počítače. Řídí, spravuje a koordinuje hlavní paměť, ALU, registry, vstupní a výstupní jednotky. Načte pokyny a generuje řídicí signály pro provedení.

2). Co je řídicí paměť?

Řídicí pamětí je obvykle RAM nebo ROM pro uložení adresy a dat řídicího registru.

3). Co je řídicí jednotka Wilkes?

Sekvenční a kombinační obvody pevně zapojené řídicí jednotky jsou nahrazeny řídicí jednotkou Wilkes. Využívá paměťovou jednotku k ukládání sekvencí pokynů mikroprogramu.

4). Co je pevně připojená řídicí jednotka?

Drátová řídicí jednotka generuje řídicí signály změnou z jednoho stavu do druhého v každém hodinovém impulsu bez jakékoli fyzické změny obvodu. Generování řídicích signálů závisí na registru instrukcí, dekodéru a přerušení signálů.

5). Co je řídicí paměť?

Informace o řídicí jednotce nebo data jsou dočasně nebo trvale uložena v řídicí paměti.

Řídicí paměť je dvou typů. Jedná se o paměť s náhodným přístupem (RAM) a paměť pouze pro čtení (ROM).

Jedná se tedy o definici, komponenty, design, diagram, funkce a typy řídicí jednotky . Zde je pro vás otázka: „Jaký je účel registru kontrolních adres?“