Proces navrhování digitálního hardwaru se za posledních několik let intenzivně proměnil. Malé digitální obvody lze tedy implementovat pomocí PAL a PLA. Používá se každé zařízení implementovat různé obvody které nepotřebují více než počet i / ps, o / ps a produktových podmínek, které jsou nabízeny v konkrétním čipu. Tyto čipy nejsou dostatečné k poměrně skromným velikostem, obvykle podporují vzájemný počet vstupů a výstupů nejvýše 32. Pro návrh těchto obvodů, které potřebují více vstupů a výstupů, lze použít buď řadu PLA / PAL, nebo klasičtější typ lze použít čip nazývaný CPLD (komplexní programovatelné logické zařízení). Čip CPLD obsahuje několik bloků obvodů na jednom čipu s vnitřními zdroji pro připojení obvodových bloků. Každý obvodový blok je srovnatelný s PLA nebo PAL.

Co je to komplexní programovatelné logické zařízení?

Zkratka CPLD je „Komplexní programovatelná logická zařízení“, je to jedna druh integrovaného obvodu které návrháři aplikací navrhují k implementaci digitálního hardwaru, jako jsou mobilní telefony. Mohou zvládnout vědomě vyšší designy než SPLD (jednoduchá programovatelná logická zařízení), ale nabízejí méně logiky než FPGA ( polní programovatelná hradlová pole ). CPLD obsahují mnoho logických bloků, každý z těchto bloků obsahuje 8–16 makrobuněk. Protože každý logický blok vykonává určitou funkci, jsou všechny makrobuňky v logickém bloku plně propojeny. V závislosti na použití mohou nebo nemusí být tyto bloky vzájemně propojeny.

Složité programovatelné logické zařízení

Většina CPLD (komplexní programovatelná logická zařízení) má makrobuňky se součtem logické funkce a volitelnou FF (klopný obvod) . V závislosti na čipu kombinatorická logická funkce podporuje 4 až 16 produktových podmínek včetně fan-in. CPLD se také liší z hlediska posuvných registrů a logických hradel. Z tohoto důvodu lze místo FPGA použít CPLD s velkým počtem logických hradel. Další specifikace CPLD označuje počet výrazů produktu, které může makrobuňka dosáhnout. Výrazy produktu jsou produktem digitálních signálů, které vykonávají konkrétní logickou funkci.

CPLD jsou k dispozici v několika formách IC balíků a logických rodinách. CPLD se také liší z hlediska napájecího napětí, provozního proudu, pohotovostního proudu a ztrátového výkonu. Kromě toho je lze získat s různým množstvím paměti a různými druhy podpory paměti. Paměť se obvykle vyjadřuje v bitech / megabitech. Podpora paměti se skládá z ROM, RAM a dual-port RAM. Skládá se také z paměti CAM (adresovatelná paměť obsahu) a FIFO (první dovnitř, první ven) a paměti LIFO (poslední dovnitř, poslední ven).

Architektura komplexního programovatelného logického zařízení

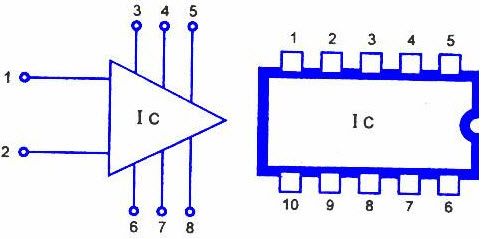

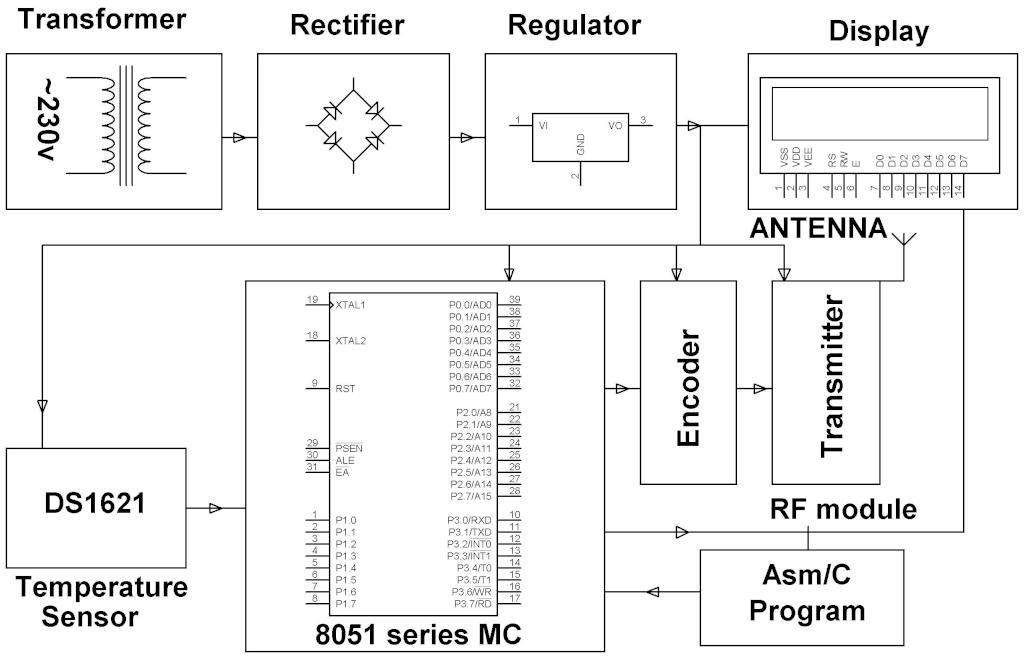

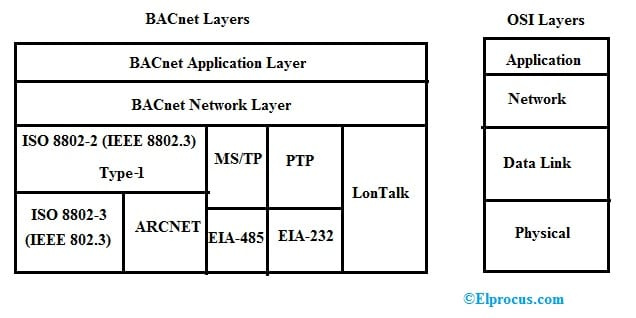

Komplexní programovatelné logické zařízení se skládá ze skupiny programovatelných FB (funkčních bloků). Vstupy a výstupy těchto funkčních bloků jsou vzájemně propojeny pomocí GIM (globální propojovací matice). Tato propojovací matice je rekonfigurovatelná, takže můžeme upravovat kontakty mezi funkčními bloky. Budou existovat některé vstupní a výstupní bloky, které nám umožní sjednotit CPLD s vnějším světem. Architektura CPLD je uvedena níže.

Programovatelný FB obecně vypadá jako řada logických bran , kde lze naprogramovat řadu bran AND a brány OR jsou stabilní. Každý výrobce má ale svůj způsob uvažování o navržení funkčního bloku. Uvedený o / p lze najít provozováním zpětnovazebních signálů získaných z výstupů brány OR.

Architektura CPLD

V programování CPLD je návrh nejprve kódován v jazyce Verilog nebo VHDL, jakmile je kód (simulován a syntetizován. Během syntézy je ručně vybrán model CPLD (cílové zařízení) a je vytvořen seznam mapovacích sítí založených na technologii. Tento seznam může být blízký - přizpůsobení se skutečné architektuře CPLD s využitím procesu místa a trasy, obvykle dosaženého softwarem typu místo a trasy společnosti CPLD Company. Poté operátor provede některé potvrzovací procesy. Pokud je vše v pořádku, použije CPLD, jinak uspořádá to.

Problémy architektury CPLD

Při zvažování složitého programovatelného logického zařízení pro použití v designu existuje několik následujících problémů s architekturou, které lze vzít v úvahu

- Programovací technologie

- Schopnost funkčního bloku

- Možnost I / O

Některé z rodin CPLD od různých maloobchodníků zahrnují

- Rodiny Altera MAX 7000 a MAX 9000

- Atmel ATF a ATV rodiny

- Rodina LSI isp Lattice

- Lattice (Vantis) MACH rodina

- Rodina Xilinx XC9500

Rodiny CPLD

Aplikace CPLD

Mezi aplikace CPLD patří následující

- Komplexní programovatelná logická zařízení jsou ideální pro vysoce výkonné aplikace s kritickým řízením.

- CPLD lze použít v digitálních designech k provádění funkcí zavaděče

- CPLD se používá k načtení konfiguračních dat pole programovatelného hradlového pole z energeticky nezávislé paměti.

- Obecně se používají v malých designových aplikacích, jako je dekódování adres

- CPLD se často používají v mnoha aplikacích, jako jsou cenově dostupná přenosná zařízení napájená z baterie kvůli jejich malé velikosti a využití nízké spotřeby.

Jedná se tedy o komplexní architekturu programovatelných logických zařízení a její aplikace. Doufáme, že jste tomuto konceptu lépe porozuměli. Kromě toho jakékoli dotazy týkající se tohoto konceptu nebo realizovat jakékoli elektrické a elektronické projekty , uveďte své cenné návrhy komentářem v sekci komentářů níže. Zde je otázka, jaký je rozdíl mezi CPLD a FPGA?

Fotografické kredity:

- CPLD wikimedia

- Architektura CPLD slidesharecdn