ECL (emitter coupled logic) byl poprvé vynalezen v IBM v srpnu 1956 Hannonem S. Yourkem. Tato logika je také známá jako logika aktuálního režimu, používaná v počítačích IBM 7090 & 7094. Rodina ECL je velmi rychlá ve srovnání s digitální logika rodiny. Obecně tato logická rodina poskytuje zpoždění šíření menší než 1 ns. Je to logická rodina založená na bipolárních tranzistorech. Je to nejrychlejší logický obvod rodiny, který je dostupný pro návrh konvenčního logického systému. Tento článek pojednává o přehledu an emitor vázaný logický obvod , práce s aplikacemi.

Co je to Emitter Coupled Logic?

Logika spojená s emitorem je nejlepší BJT -založená logická rodina používaná v konvenčním návrhu logického systému. Někdy se také nazývá logika aktuálního režimu, což je velmi vysokorychlostní digitální technologie. Obecně je ECL považován za nejrychlejší logický IC, kde dosahuje svého vysokorychlostního provozu pomocí velmi malého kolísání napětí a také zamezení vstupu tranzistorů do oblasti saturace.

Implementace ECL využívá kladné napájecí napětí, které je známé jako PECL nebo ECL s kladnou referencí. U časných hradel ECL se používá záporné napětí kvůli odolnosti proti šumu. Poté se ECL s kladnými referencemi stalo velmi slavným díky svým kompatibilnějším logickým úrovním ve srovnání s logickými rodinami TTL.

Emitorově vázaná logika rozptyluje obrovské množství statického výkonu, ale její celková spotřeba proudu je ve srovnání s CMOS na vysokých frekvencích. ECL je tedy prospěšné hlavně v obvodech distribuce hodin a aplikacích založených na vysokých frekvencích.

Logické funkce spojené s emitorem

Díky funkcím ECL budou použity v mnoha vysoce výkonných aplikacích.

- ECL poskytuje dva výstupy, které se vždy vzájemně doplňují, protože činnost obvodu je založena na diferenciálním zesilovači.

- Tato logická rodina je vhodná hlavně pro monolitické způsoby výroby, protože logické úrovně jsou funkcí poměrů rezistorů.

- Zařízení řady ECL generují správný a doplňkový výstup navrhované funkce bez použití jakýchkoliv externích měničů. V důsledku toho snižuje počet balíčků a požadavky na napájení a také snižuje problémy vznikající z časových zpoždění.

- Zařízení ECL v designu diferenciálního zesilovače nabízejí širokou výkonnostní flexibilitu, takže obvody ECL umožňují použití jako digitální i lineární obvody.

- Konstrukce brány ECL má normálně vysokou a nízkou vstupní impedanci, což extrémně přispívá k dosažení velkého výstupu ventilátoru a také schopnosti měniče.

- Zařízení ECL generují konstantní odběr proudu na napájecím zdroji, aby se zjednodušil návrh napájecího zdroje.

- Zařízení ECL včetně výstupů s otevřeným emitorem jim jednoduše umožňují zahrnout kapacitu pohonu přenosové linky.

Emitor vázaný logický obvod

Níže je zobrazen logický obvod s emitorem pro invertor, který je navržen s odpory a tranzistory. V tomto obvodu jsou terminály emitoru dvou tranzistorů jednoduše připojeny k odporu RE omezujícímu proud, který se používá k zabránění vstupu tranzistoru do saturace. Zde je výstup tranzistoru odebírán z kolektorového terminálu namísto terminálu emitoru. Tento obvod poskytuje dva výstupy Vout (invertující výstup) a Vout2 (neinvertující výstup) a vstupní svorku jako Vin, kde je dán vysoký nebo nízký vstup. +Vcc = 5V.

Jak funguje logika spřažená s emitorem?

Funkce logiky spojené s emitorem je taková, že kdykoli je do obvodu ECL přiveden vstup HIGH, pak se tranzistor „Q1“ zapne a tranzistor Q2 vypne, ale tranzistor Q1 není saturován. Takže to vytáhne výstup VOUT2 na HIGH a hodnota výstupu VOUT1 bude LOW kvůli poklesu v R1.

Podobně, když je hodnota VIN přidělená ECL NÍZKÁ, pak bude tranzistor Q1 vypnutý a tranzistor Q2 zapnutý. Takže tranzistor Q2 nepřejde do saturace. Takže to způsobí, že výstup VOUT1 bude vytažen na vysokou hodnotu a výstupní hodnota VOUT2 bude nízká kvůli poklesu odporu R2.

Podívejme se, jak se tranzistor Q1 a Q2 zapíná a vypíná, když je přivedeno napětí.

Dva tranzistory jako Q1 a Q2 v tomto obvodu jsou spojeny jako diferenciální zesilovač rezistorem se společným emitorem.

Zdroje napětí pro tento příklad obvodu jsou VCC = 5,0, VBB = 4,0 & VEE = 0 V. Hodnoty vstupní úrovně HIGH & LOW jsou jednoduše definovány jako 4,4 V & 3,6 V. Ve skutečnosti tento obvod generuje úrovně LOW a HIGH, které jsou o 0,6 V vyšší; toto je však opraveno v rámci skutečných obvodů ECL.

Jakmile je Vin VYSOKÝ, pak je tranzistor Q1 zapnutý, ale není nasycený a tranzistor Q2 je vypnutý. Takže výstupní napětí jako VOUT2 je taženo na 5 V přes rezistor R2 a lze ukázat, že úbytek napětí na rezistoru R1 je asi 0,8 V, takže VOUT1 = 4,2 V (LOW). Navíc VE = VOUT1 – VQ1 => 4,2 V – 0,4 V = 3,8 V, protože tranzistor Q1 je zcela zapnutý.

Jakmile je Vin LOW, tranzistor Q2 se zapne, ale nebude nasycen a tranzistor Q1 se vypne. Proto je VOUT1 natažen na 5,0 V pomocí rezistoru R1 a lze ukázat, že VOUT2 je 4,2 V. Také VE => VOUT2 – VQ2 => 4,2 V – 0,8 V => 3,4 V, když je tranzistor Q2 zapnutý.

V ECL nejsou dva tranzistory nikdy v saturaci jako t kolísání vstupního / výstupního napětí je poměrně malé, například 0,8 V a vstupní impedance je vysoká a výstupní odpor je nízký. To pomáhá ECL pracovat rychleji s kratší dobou zpoždění šíření.

Logický obvod OR/NOR se dvěma vstupy a emitorem

Obvod logického hradla OR/NOR se dvěma vstupy s emitorem je zobrazen níže. Tento obvod je navržen úpravou výše uvedeného obvodu invertoru. Úprava spočívá v přidání dalšího tranzistoru na vstupní stranu.

Fungování tohoto obvodu je velmi jednoduché. Když jsou vstupy na obou tranzistorech Q1 a Q2 nízké, pak výstup1 (Vout1) bude mít hodnotu HIGH. Toto Vout1 tedy odpovídá výstupu brány NOR.

Současně, pokud je tranzistor Q3 zapnutý, pak druhý výstup (Vout2) bude VYSOKÝ. Tento výstup Vou2 tedy odpovídá výstupu hradla OR.

Stejným způsobem, pokud jsou oba vstupy tranzistorů Q1 & Q2 VYSOKÉ, pak sepne tranzistory Q1 a Q2 a poskytuje nízký výstup na svorce VOUT1.

Pokud je tranzistor Q3 během této operace vypnutý, bude poskytovat vysoký výstup na svorce VOUT2. Takže pravdivostní tabulka pro hradlo OR/NOR je uvedena níže.

|

Vstupy |

Vstupy | NEBO |

ANI |

|

A |

B | Y | Y |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

Emitorově vázané logické charakteristiky

Charakteristiky ECL zahrnují následující.

- Ve srovnání s TTL má ECL rychlejší dobu šíření v rozmezí od 0,5 do 2 ns. Ale ztrátový výkon logiky spojený s emitorem je vyšší ve srovnání s TTL, například 30 mW.

- I/O napětí ECL mají malý výkyv jako 0,8.

- Vstupní impedance ECL je vysoká a výstupní odpor je nízký; v důsledku toho tranzistor mění své stavy velmi rychle.

- Kapacita ventilátoru ECL je vysoká a zpoždění brány je nízké.

- O/p logika ECL se mění ze stavu LOW do stavu HIGH, ale úrovně napětí pro tyto stavy se budou lišit mezi TTL a EC.

- Odolnost proti rušení ECL je 0,4V.

Výhody a nevýhody

The výhody logiky spojené s emitorem jsou diskutovány níže.

- Fanout ECL je 25, což je lepší ve srovnání s TTL a je nízké ve srovnání s CMOS.

- Průměrná doba zpoždění šíření ECL je 1 až 4 ns, což je lepší ve srovnání s CMOS a

- TTL. Proto se nazývá nejrychlejší logická rodina.

- Když se BJT v emitoru spřaží logická hradla pracují v aktivní oblasti, pak mají maximální rychlost ve srovnání se všemi logickými rodinami.

- ECL brány generují doplňkové výstupy.

- V napájecích vodičích nejsou proudové spínací špičky.

- Výstupy mohou být propojeny společně pro zajištění funkce drátového NEBO.

- Parametry ECL se vlivem teploty příliš nemění.

- Ne. počet funkcí přístupných z jediného čipu je vysoký.

The nevýhody logiky spřažené s emitorem jsou diskutovány níže.

- Má extrémně menší šumovou rezervu, tj. ±200 mV.

- Ztrátový výkon je vysoký ve srovnání s jinými logickými hradly.

- Pro propojení s jinými logickými rodinami jsou nutné posunovače úrovní.

- Fanout omezuje kapacitní zatížení.

- Ve srovnání s TTL , ECL brány jsou drahé.

- Ve srovnání s CMOS a TTL je odolnost proti hluku ECL nejhorší.

Aplikace

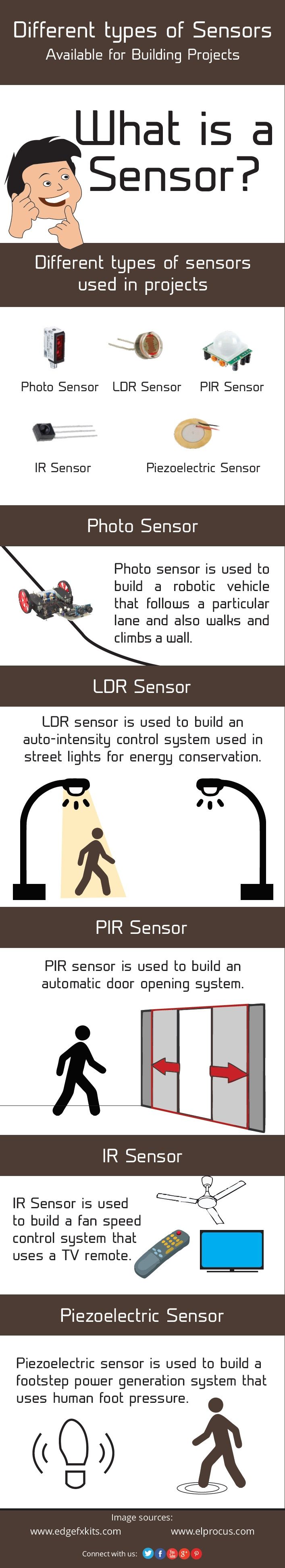

Aplikace logiky spojené s emitorem zahrnují následující.

- Logika spřažená s emitorem se používá jako logika a technologie rozhraní v extrémně vysokorychlostních komunikačních zařízeních, jako jsou optická rozhraní transceiveru, sítě Ethernet a ATM (Asynchronous Transfer Mode).

- ECL je logická rodina založená na BJT, kde lze dosáhnout vysokorychlostního provozu použitím relativně malého kolísání napětí a zabráněním pohybu tranzistorů do oblasti saturace.

- ECL se používá při výrobě obvodů ASLT v rámci IBM 360/91.

- ECL se vyhýbá použití vrstvených tranzistorů použitím jednostranného předpětí i/p a kladné zpětné vazby mezi primárními a sekundárními tranzistory k dosažení funkce invertoru.

- ECL se používá v extrémně vysokorychlostní elektronice.

Tedy, toto je přehled logiky spojené s emitorem nebo ECL – obvod, funkce, vlastnosti, charakteristiky a aplikace. ECL je velmi nejrychlejší logická rodina založená na BJT ve srovnání s jinými digitálními logickými rodinami. Dosahuje své maximální rychlosti provozu pomocí malého kolísání napětí a zabránění pohybu tranzistorů do oblasti nasycení. Tato logická rodina poskytuje neuvěřitelné zpoždění šíření 1ns a v nejnovějších rodinách ECL je toto zpoždění sníženo. Zde je otázka pro vás, jaký je alternativní název pro ECL?