Hlavní nevýhodou kombinační obvod to znamená, že nepoužívá žádnou paměť k uložení současného a předchozího stavu. Předchozí stav vstupu proto nemá žádný vliv na současný stav obvodu. Zatímco sekvenční obvod má paměť, takže výstup se může lišit v závislosti na vstupu. Tento typ obvodů využívá předchozí vstup, výstup, hodiny a paměťový prvek. Zde mohou být paměťovými prvky západky nebo klopné obvody. Sekvenční obvody jsou navrženy různými metodami, jako je použití ROM a Flips, PLA, CPLD (Complex Programmable Logic Device) , FPGA (Field Programmable Gate Array) . V tomto článku budeme diskutovat pouze o tom, jak navrhnout sekvenční obvod pomocí PLA.

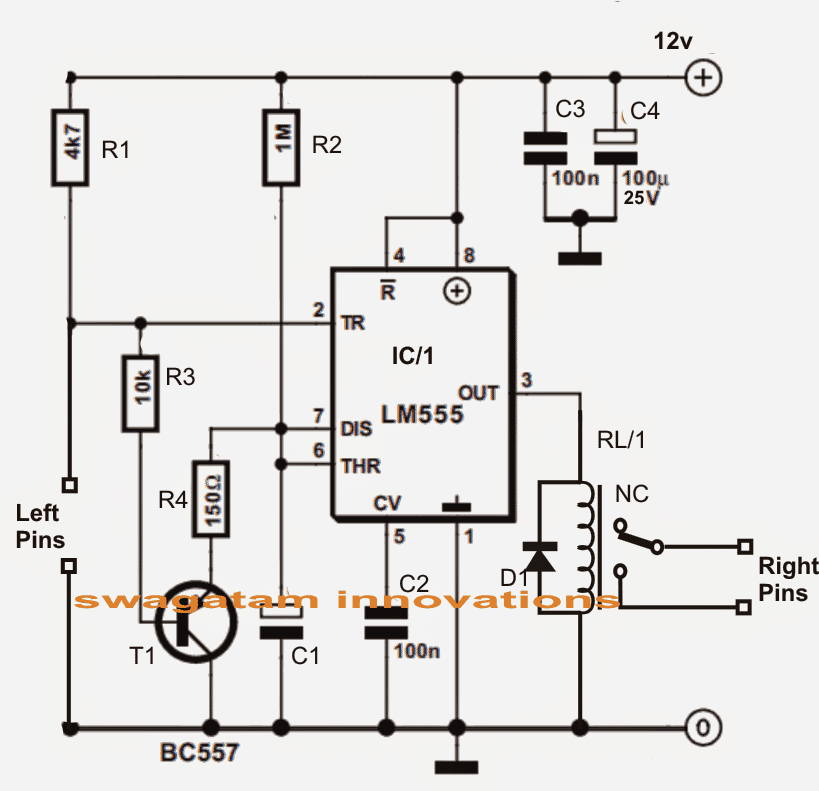

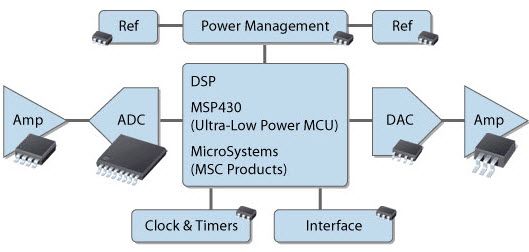

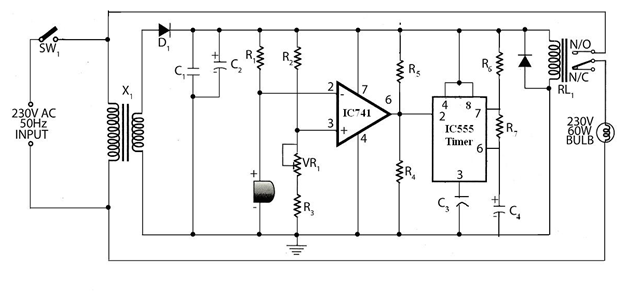

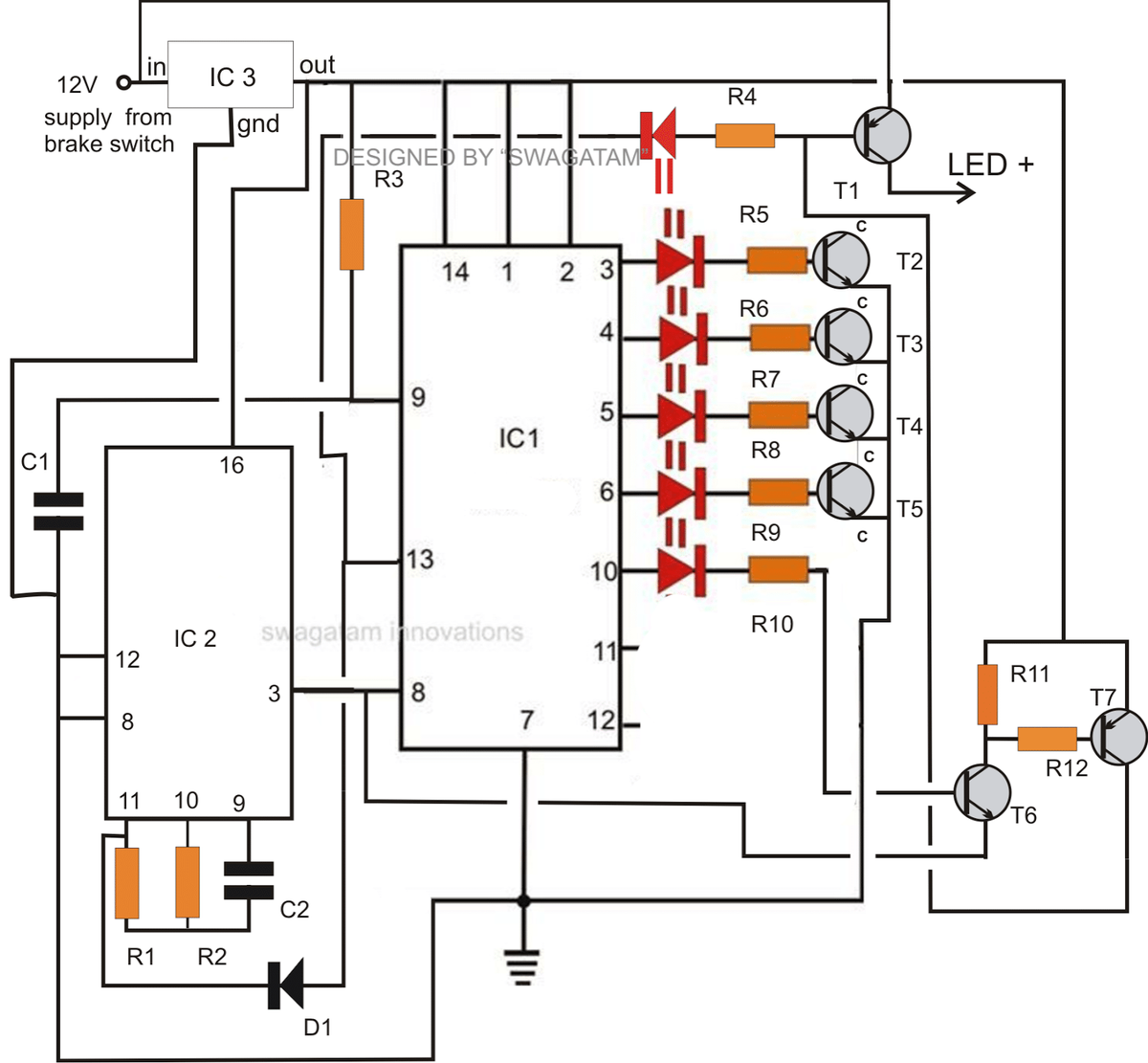

Blokové schéma sekvenčního obvodu, jak je znázorněno níže:

Blokové schéma sekvenčního obvodu

Návrh sekvenčního obvodu pomocí PLA

Sekvenční obvody lze realizovat pomocí PLA (Programmable Logic Arrays) a klopných obvodů. V tomto návrhu může být přiřazení stavu důležité, protože použití přiřazení dobrého stavu může snížit požadovaný počet výrazů produktu, a tím snížit požadovanou velikost PLA. Termín produktu definovaný jako spojení literálů, kde každý literál je buď proměnná, nebo její negace.

Uvažujme design o převaděč kódu. Stavovou tabulku zobrazenou níže v tabulce lze realizovat pomocí jedné PLA a tří žabky jak je znázorněno níže na obrázku. Tato konfigurace obvodu je velmi podobná návrhu klopného obvodu ROM, až na to, že ROM je nahrazen PLA vhodné velikosti. Přiřazení stavu vede k níže uvedené tabulce pravdivosti. Tato tabulka by mohla být uložena v PLA se čtyřmi vstupy, 13 výrazy produktu a čtyřmi výstupy, ale ve srovnání s 16slovnou ROM by to nabídlo jen malou velikost.

| X Q1 Q2 Q3 | S D1 D2 D3 |

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 | 1 0 0 1 1 0 1 1 0 1 0 0 0 1 0 1 1 1 0 1 0 0 0 0 1 0 0 0 X X X X. 0 0 1 0 0 1 0 0 1 1 0 0 1 1 0 1 0 1 1 0 1 0 0 0 X X X X. X X X X. |

Tabulka: Tabulka pravdy

SOUČASNOST, DÁREK STÁT

| DALŠÍ STAV X = 0,1 | SOUČASNOST, DÁREK VÝSTUP (Z) |

| NA | PŘED NAŠÍM LETOPOČTEM | 1 0 |

B C | D E A E. | 1 0 0 1 |

D JE | H H H M | 0 1 1 0 |

H M | A A DO - | 0 1 1 - |

Tabulka: Tabulka stavů

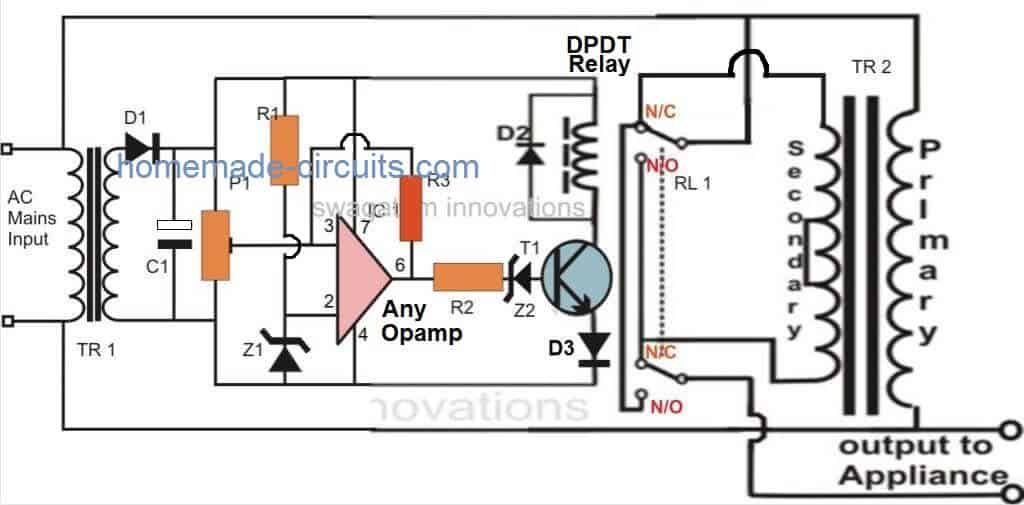

Navrhování sekvenčních obvodů pomocí PLA

Rovnice vstupního výstupu odvozené z Karnaughovy mapy

Tady, protože existuje sedm stavů, jsou vyžadovány tři klopné obvody typu D. Je tedy vyžadován obvod PLA se 4 vstupy a 4 výstupy. Pokud se vezme v úvahu stavové přiřazení převaděče kódu, výslednou výstupní rovnici a vstupní klopné rovnice D odvozené z Karnaugha lze napsat následující rovnice

D1 = Q1 + = Q2 ”

D2 = Q2 + = Q2 ”

D3 = Q3 + = Q1 Q2 Q3 = X ”Q1 Q3” = X Q1 ”Q2”

Z = X ”Q3” + X Q3

| X Q1 Q2 Q3 | S D1 D2 D3 |

- - 0 - - 1 - - - 1 1 1 0 1 - 0 100 - 0 - - 0 jedenáct

| 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0

|

Tabulka PLA, která odpovídá těmto rovnicím, je uvedena v tabulce výše. Tuto tabulku lze realizovat pomocí PLA se čtyřmi vstupy, sedmi výrazy produktu a čtyřmi výstupy. Chcete-li nejprve ověřit fungování výše uvedeného návrhu, předpokládejme, že X = 0 a Q1Q2Q3 = 000. Tím se v tabulce vyberou řádky - - 0- a 0 - - -0, takže Z = 0 a D1D2D3 = 100. Po aktivní hodinové hraně Q1Q2Q3 = 100. Pokud je další vstup X = 1, jsou vybrány řádky - - 0 - a - 1- -, takže Z = 0 a D1D2D3 = 110. Po aktivní hodinové hraně Q1Q2Q3 = 110.

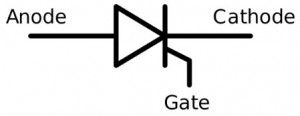

Programovatelné logické pole (PLA)

Programmable Logic Array je programovatelné logické zařízení. Obvykle se používá k implementaci kombinačních logických obvodů. PLA má sadu programovatelných rovin AND (pole AND), které odkazují na sadu programovatelných rovin OR (pole OR), které lze poté prozatímně doplnit za účelem vytvoření výstupu. Toto rozvržení umožňuje syntetizovat velké množství logických funkcí v systému součet produktů (SOP) kanonické formy. Níže je uvedeno jednoduché blokové schéma PLA.

Blokové schéma PLA

Hlavní rozdíl mezi PLA a PAL (programovatelná logika pole) je,

PLA: Oba AND letadlo a OR letadlo jsou programovatelné.

PAL: Programovatelná je pouze rovina AND, zatímco rovina OR je pevná.

Pro lepší pochopení PLA zde uvažujeme níže uvedený příklad.

Zkusme implementovat tyto funkce f1 a f2 jsou uvedeny jako

Vstupy x1, x2, x3 a jejich příslušné doplňované signály jsou dány programovatelné rovině AND, kde dostaneme výstupy roviny AND jako mintermy zvané P1, P2, P3. Poté jsou tyto signály předány programovatelné rovině OR pro vytvoření požadované výstupní funkce f1 a f2 (součet produktů). Níže uvedený obrázek popisuje implementaci PLA na úrovni brány pro danou funkčnost.

Provádění CHKO

Jedná se o návrh sekvenčních obvodů pomocí PLA. Domníváme se, že informace uvedené v tomto článku vám pomohou lépe porozumět tomuto konceptu. Kromě toho jakékoli dotazy týkající se tohoto článku nebo pomoc v provádění projektů v oblasti elektrotechniky a elektroniky , můžete nás kontaktovat komentováním v sekci komentářů níže. Zde je otázka pro vás, Co se rozumí sekvenčním obvodem?