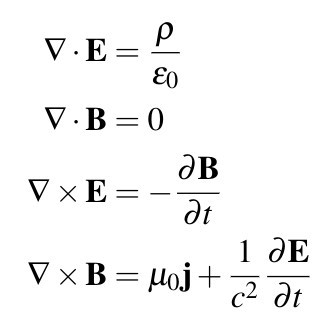

Termín VLSI znamená „Very Large Scale Integration Technology“, která zahrnuje návrh integrovaných obvodů (IC) kombinací tisíců tranzistory logicky do jednoho čipu do různé logické obvody . Tyto integrované obvody nakonec snižují obsazený prostor obvodů ve srovnání s obvody s konvenčními obvody. Výpočetní výkon a využití prostoru jsou hlavními výzvami návrhu VLSI. Implementace projektů VLSI otevírá náročnou a jasnou kariéru pro studenty i výzkumné pracovníky. Některé z nových trendových oblastí VLSI jsou Polní programovatelné hradlové pole aplikace (FPGA), návrhy ASIC a SOC. Níže je uveden seznam některých projektů VLSI pro ty studenty, kteří vážně hledají projekty v této oblasti. Tento článek pojednává o přehledu projektů VLSI založených na FPGA, Xilinx, IEEE, Mini, Matlab atd., Které jsou uvedeny níže. Tyto projekty jsou velmi užitečné pro studenty inženýrství, studenty M.tech.

Projekty VLSI pro studenty inženýrství

Níže jsou diskutovány projekty VLSI s abstrakty pro studenty elektronického inženýrství.

Projekty VLSI

1). Transformace diskrétní vlnky založená na 3D zvedání

Tento projekt pomáhá při zajišťování vysoce přesných obrazů pomocí kódování obrazu bez ztráty jeho dat. K dosažení tohoto cíle tento proces implementuje zvedací filtr v závislosti na transformaci 3D diskrétní vlnkové architektury VLSI.

2). Návrh multiplikátoru SFQ s 4bitovým efektem pomocí vysokorychlostního hardwaru

Tento projekt se používá hlavně k implementaci upraveného kodéru stánku (MBE) na bázi 4bitového SFQ násobitel . Tento multiplikátor poskytuje dobrý výkon ve srovnání s konvenčním kodérem stánku. Tento projekt se používá hlavně v aplikacích kritického zpoždění.

3). Kryptografický procesor používaný na čipových kartách s efektivní oblastí

Tento projekt se používá k implementaci tří kryptografických algoritmů podporovaných jak soukromými, tak veřejnými klíči používanými v chytrá karta aplikace pro poskytování extrémně zabezpečeného ověření a dat uživatele sdělení .

4). Vysokorychlostní nebo nízkoenergetický multiplikátor s metodou potlačení rušivého výkonu

Tento navrhovaný systém filtruje zbytečné falešné signály aritmetických jednotek, aby se zabránilo zbytečnému přenosu dat, který neovlivňuje poslední výsledky výpočtu. Tento systém používá metodu SPST pro multiplikátory k dosažení nízkého výkonu a vysokorychlostního přenosu dat.

5). Komprese a dekomprese bezztrátového datového algoritmu

Tento projekt je implementován hlavně pro dvoustupňovou hardwarovou architekturu v závislosti na funkci algoritmu PDLZW (Parallel Dictionary LZW) a algoritmu typu Adaptive Huffman, který se používá jak pro aplikace bezztrátové komprese dat, tak bezztrátové dekomprese.

6). Architektura Turbo dekodéru s nízkou složitostí pro energeticky účinné WSN

Navrhovaný systém se používá ke snížení celkové spotřeby energie při přenosu dat WSN prostřednictvím algoritmu rozkládání LUT-Log-BCJR na základní operace ACS (Přidat Porovnat Vybrat).

7). Architektura VLSI pro efektivní odstranění impulzního šumu obrazu

Tento navrhovaný systém se používá hlavně k vizuálnímu zlepšení kvality obrazu, aby se předešlo riziku poškození impulsním šumem k implementaci efektivní architektury VLSI pomocí filtru na ochranu hran.

8). Architektura procesoru v paměti používaného pro kompresi multimédií

Tento navrhovaný systém poskytuje architekturu s nízkou složitostí procesor v paměti pro podporu multimediálních aplikací, jmenovitě komprese obrazu, videa pomocí enormní jediné instrukce, více datových konceptů a instrukčního slova.

9). Technika synchronizace časování se symbolovou rychlostí pro bezdrátové systémy OFDM s nízkou spotřebou

Tento navrhovaný systém se používá hlavně ke zlepšení činnosti bezdrátového OFDM (Orthogonal Frequency Division Multiplexování ) prostřednictvím snižování výkonu celého základního pásma pomocí hodin generátor s fázově laditelným a dynamickým řadičem časování vzorků.

10). Nízkoenergetická a vysokorychlostní implementace multiplikátoru na bázi akumulátoru pomocí programu SPST Adder a Verilog

Tento projekt se používá k návrhu nízkoenergetického a vysokorychlostního MAC (multiplikátoru a akumulátoru) prostřednictvím přijetí metody falešného potlačení energie na MBE (modifikovaný kodér stánku). Použitím této konstrukce lze zabránit ztrátě energie celého přepínání.

11). Návrh a implementace robotického procesoru umožněním antikolizí s technologií RFID

Navrhovaný systém se používá hlavně k implementaci robotického procesoru s antikolizí, aby se zabránilo fyzické kolizi robotů v prostředí multi-robota. Tento algoritmus je implementován hlavně pomocí technologie VHDL a RFID.

12). Návrh logického obvodu s energetickou účinností pomocí adiabatické metody

Tento systém demonstruje design logických obvodů efektivně pomocí adiabatické metody ve srovnání s konvenčním designem CMOS pomocí obvodů využívajících Brány NAND & NOR . Použitím adiabatické metody lze snížit rozptyl energie v síti a recyklovat uloženou energii v zátěžovém kondenzátoru.

3). Šifrovací systém pro zvýšení výpočetní rychlosti systému

Hlavním záměrem tohoto projektu je zvýšit zabezpečení přenosu dat a zlepšit rychlost výpočtu implementací algoritmu AES pomocí FPGA. Tuto simulaci, stejně jako matematický design, lze tedy provést pomocí kódu VHDL.

14). IP blok AHM nebo Advanced High-Performance Bus

Tento projekt se používá hlavně k návrhu architektury Advanced Mikrokontrolér Bus (AMB) pomocí AHBN (Advanced High-Performance Bus). Tento projekt může být navržen s kódem VHDL implementací bloků jako master & save.

15). Multimode RF Transceiver založený na DSM s vícekanálovým

Tento systém se používal hlavně k návrhu multimódové architektury vysílače a přijímače a vícekanálového RF s modulátorem Delta-Sigma. Tento navrhovaný systém používá jazyk VHDL k implementaci dvou architektur.

16). Koncentrátor vyřazovacího přepínače pomocí režimu asynchronního přenosu

Pomocí tohoto projektu lze pomocí nástrojů, jako jsou VHS a VHDL, navrhnout knockoutový přepínač založený na asynchronním přenosu. Tento knock-out přepínač lze použít v sítích paketů virtuálních obvodů i v aplikacích datagramu.

17). Asynchronní obvody Behaviorální syntéza

Tento projekt se používá hlavně k poskytnutí techniky syntézy chování používané pro asynchronní obvody. Obě šablony, jako jsou balsová a asynchronní implementace, jsou hlavními prvky v návrhu.

18). Návrh AMBA pomocí vyhovujícího řadiče paměti AHB

Tento projekt se používá k návrhu MC (řadiče paměti) v závislosti na AMBA (Advanced Microcontroller Bus Architecture) pro řízení systémové paměti pomocí hlavní paměti, jako je SRAM a ROM.

19). Provádět implementaci sčítače stromů

Carry tree sčítač založený na VLSI designu jsou označovány jako nejlepší přidávání výkonu na rozdíl od obvyklých binárních sčítání. Mezi doplňky, které tento projekt implementuje, patří spanning tree, kogge-stone a sparse kogge-stone.

20). CORDIC Designová rotace pevného úhlu

Hlavní koncepcí tohoto navrhovaného systému je otáčení vektorů pomocí pevných úhlů. Tyto úhly jsou nezbytné pro hry, robotiku, zpracování obrazu atd. Použitím tohoto projektu lze dosáhnout rotace vektoru pomocí konkrétních úhlů podle návrhu CORDIC (digitální počítač s rotací souřadnic).

21). Návrh filtru FIR s distribuovanou aritmetikou vyhledávací tabulky

Tento navrhovaný systém hlavně vylepšuje FIR filtr výkon tím, že jej namísto multiplikátoru navrhnete pomocí distribuované aritmetiky trojrozměrné vyhledávací tabulky. Tento návrh lze tedy implementovat pomocí softwaru jako FPGA a Xilinx.

22). Push-Pull pulzní západky s vysokou rychlostí a podmíněným nízkým výkonem

Tento projekt se používá k provedení energeticky účinných a vysoce výkonných pulzních západek používaných hlavně pro systémy VLSI pomocí nové topologie. Protože tato topologie závisí hlavně na konečné fázi push-pull poháněné pomocí dvou dělících pruhů prostřednictvím podmíněného generátoru impulzů.

23). Architektura aritmetického kodéru VLSI v SPIHT

Tento navrhovaný systém zvyšuje propustnost metody aritmetického kódování při komprimaci obrazu dělení v hierarchických stromech (SPIHT) s vysokorychlostní architekturou v závislosti na FPGA.

24). Potlačení šumu signálu EKG na základě FPGA

Tento projekt slouží k zachycení šumu v EKG signálech prostřednictvím dvou středních filtrů s velikostí 91 a 7 vzorkovacích bodů. Tento proces lze tedy dosáhnout implementací Návrh FPGA na základě kódu VHDL.

25). Vysoce výkonný procesor pro škálování obrazu založený na VLSI s nízkými náklady

Tento projekt se používá k implementaci algoritmu pro procesor škálování obrázků založený na VLSI s menší pamětí a vysokým výkonem. Navrhovaný návrh systému obsahuje zejména kombinaci filtru, rekonfigurovatelných dynamických metod a sdílení hardwaru za účelem snížení nákladů.

26). Efektivní návrh a implementace architektury systolického pole

Hlavním konceptem tohoto projektu je návrh hardwarového modelu používaného pro multiplikátor systolického pole. Toto pole lze použít hlavně k provádění binárního násobení pomocí platformy VHDL. Navrhovaný návrh systému lze implementovat pomocí softwaru FPGA & Isim.

27). QPSK Design & Synthesis using VHDL Code

QPSK je jednou z hlavních modulačních metod. Tato metoda se používá v aplikacích satelitního rádia. Tuto modulační techniku lze implementovat pomocí vratných logických bran. Návrh techniky QPSK lze provést pomocí kódu VHDL.

28). Návrh a implementace řadiče DDR SDRAM s vysokou rychlostí

Navrhovaný systém se používá k návrhu řadiče DDR SDRAM pro přenos sériových dat v závislosti na vysoké rychlosti k synchronizaci těchto dat mezi obvody vestavěného systému a DDR SDRAM. Pomocí jazyka VHDL lze kód vyvinout.

29). 32bitový návrh a implementace procesoru RISC

Hlavním konceptem tohoto projektu je implementace 32 bitů RISC (počítač se sníženou instrukční sadou) pomocí nástroje jako XILINK VIRTEX4. V tomto projektu je navrženo 16 instrukčních sad všude, kde lze každou instrukci provést v jednom cyklu CLK pomocí metody pětifázového pipeline.

30). Implementace sběrnicového mostu mezi AHB a OCP

Navrhovaný systém se používá k návrhu sběrnicového mostu mezi dvěma protokoly, a to běžným a standardním. Velmi populární jsou komunikační protokoly jako AHB (Advanced High-performance Bus) & OCP (Open Core Protocol), které se používají v aplikacích SoC (systémový čip) .

Nápady na projekty VLSI pro studenty inženýrství

Seznam projektů VLSI založených na FPGA, MatLab, IEEE a Mini Projects pro studenty inženýrství je uveden níže.

Projekty VLSI pro studenty M. Tech

Seznam projektů VLSI založených na M. Tech Students zahrnuje následující.

- Oblastově efektivní a vysoce spolehlivý design paměťových buněk I0T založený na RHBD používaný v leteckých aplikacích

- Fázový detektor s víceúrovňovou poloviční rychlostí používaný pro obvody CLK a obnova dat

- Komparátor s nízkou spotřebou a vysokou rychlostí používaný pro přesné aplikace

- Převodník úrovně hradlového napětí s vysoce výkonným a integrovaným multiplexorem

- CNTFET ternární zmije s vysokým výkonem

- Návrh komparátoru velikosti s nízkou spotřebou

- Návrh prahové logické brány s proudovým režimem pro analýzu zpoždění

- Návrh dekodérů se smíšenou logikou s nízkou spotřebou a vysokým výkonem

- Návrh logické testovatelnosti spánkové konvence

- Posuvník úrovně napětí pro aplikace s dvojím napájením s vysokou rychlostí a účinností

- Návrh a analýza komparátoru s nízkým výkonem a nízkým napětím

- Flip-Flop design založený na pulsním spouštění s nízkou spotřebou energie pomocí metody průchodu signálu

- Efektivní návrh obvodů založený na RETTIME rekonfigurovatelných FET

- Návrh komparátoru velikosti s nízkou spotřebou

- Zpožděná analýza návrhů logických bran s prahovou hodnotou v aktuálním režimu

The Projekty VLSI založené na FPGA pro studenty strojírenství a CMOS VLSI designové mini-projekty jsou uvedeny níže.

- Návrh a charakterizace tvrzených obvodů SEU pro FPGA na základě SRAM

- Kompaktní CMOS hybridní CMOS hybridní LUT Design & Potenciální aplikace používaná v FPGA

- Ultrazvukové senzory Implementace FPGA pro měření vzdálenosti

- Implementace FPGA pro Booth Multiplier s FPGA Spartan6

- Diskrétní vlnková transformace založená na zvedání pomocí Spartan3 FPGA

- Řadič ARM v robotice využívající FPGA

- FPGA založené na UART s vícekanálovým

- Potlačení šumu EKG signálu pomocí FPGA

- Implementace FPGA založená na UTMI a vrstva protokolu USB 2.0

- Implementace Median filtru s Spartan3 FPGA

- Implementace FPGA založená na algoritmu AES

- Bezpečnostní výstražný systém založený na PIC pro implementaci FPGA se Spartan 3an

- Implementace FPGA k návrhu řadiče pro systémy dálkového průzkumu Země

- Sada pro zpracování obrazu FPGA využívající filtrování obrazu lineární a morfologické

- Implementace Medical Fusion Image na základě Spartan3 FPGA

Seznam Mini projekty VLSI využívající kód VHDL zahrnuje následující.

- Komparátor s vysokou rychlostí pomocí VLSI

- Multiplikátor s plovoucí desetinnou čárkou pomocí VLSI

- Převod binární na šedou na základě VLSI

- Digitální filtr

- CLK Gating založený na VLSI

- Védský multiplikátor

- CMOS FF pomocí VLSI

- Architektura paralelního procesoru využívající VLSI

- Plný sčítač založený na VLSI

- Návrh paměti DRAM / dynamického náhodného přístupu na základě VLSI

- Rozložení SRAM založené na VLSI

- Procesor digitálního signálu založený na VLSI

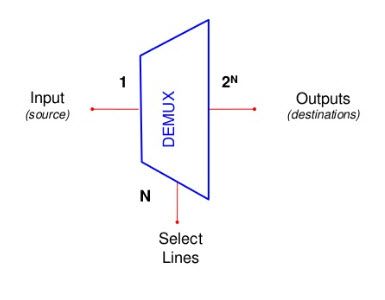

- Multiplexer založený na VLSI

- Návrh jednotky MAC na základě VLSI

- Diferenciátor založený na VLSI

- FFT založená na VLSI nebo rychlá Fourierova transformace

- Architektura diskrétní kosinové transformace založená na VLSI

- 16bitový návrh multiplikátoru pomocí VLSI19

- Návrh VIFI vyrovnávací paměti FIFO

- Vysokorychlostní akcelerátor založený na VLSI

Projekty VLSI využívající MATLAB a Xilinx

Seznam projektů VLSI založených na projektech MATLAB a VLSI pomocí Xilinx obsahuje následující.

- Návrh a analýza modemu CDMA s MATLAB

- Návrh filtru FIR pomocí VHDL na analýze založené na FPGA a MATLAB

- Simulace systému pro automobilové inženýrství založená na ModelSim & Matlab nebo Simulink

- Doplňky založené na Xilinx jako Ripple Carry & Carry Skip

- Aritmetická jednotka založená na 32bitovém plovoucím bodu

- Plovoucí bodová ALU

- RISC procesor založený na 32-bit

- Konvoluční schopnosti ortogonálního kódu

- Prodejní automat na bázi Xilinx a Verilog

- Xilinx založené paralelní předpony s 256-bit

- Protokol pro vzájemné ověřování pomocí Xilinx

- Přístup ke struktuře s jedním cyklem pro logický test pomocí Xilinx

- UTMI a protokolová vrstva založená na USB2.0 pomocí Xilinx

- Konfigurace komprese a dekomprese dat pomocí Xilinx FPGA

- Xilinx 4000 na bázi BIST a FPGA na bázi Spartan Series

- IIR filtr založený na MATLABu a VLSI

- FIR filtr pomocí MATLABu

Projekty IEEE

The seznam projektů IEEE VLSI je uveden níže.

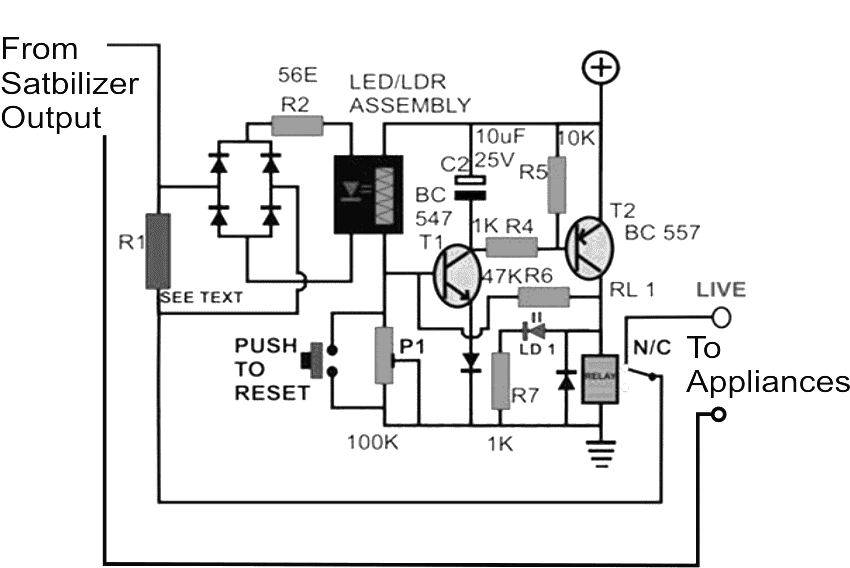

- Bezdrátový domácí automatizační systém založený na VLSI pomocí Bluetooth

- Odstranění impulzního šumu v obraze pomocí efektivní architektury VLSI

- Architektura procesoru v paměti pro multimediální kompresi

- Monitorování teplotního systému pomocí cloudu a internetu věcí

- Implementace systému OFDM s IFFT a FFT

- Hamming Code Design & Implementation with Verilog

- Rozpoznávání otisků prstů založené na VHDL pomocí Gaborova filtru

- Aritmetické funkce Přemapování pomocí ROM v závislosti na přibližných přístupech

- Analýza vysoké účinnosti a nízkohustotního výkonu dekodéru pro kontrolu parity v aplikacích s nízkou spotřebou

- FFT Architectures with Feedforward of Pipelined Radix-2k

- Návrh klopných obvodů pro aplikace VLSI využívající technologii CMOS s vysokým výkonem

- Návrh filtru FIR s vyhledávací tabulkou podle distribuované aritmetiky

- Nízko nákladový a vylepšený procesor pro škálování obrazu založený na VLSI

- Implementace a design ASIC pokročilého kodéru a dekodéru Turbo s 3GPP LTE

- Pulzní západky Push-Pull s podmíněným nízkým výkonem a vysokou rychlostí

- Vylepšené skenování při testování skenování s nízkou spotřebou

- Architektura aritmetického kodéru VLSI pro SPIHT

- Implementace VHDL pro UART

- Regulátor napětí založený na VLSI s nízkým výpadkem

- Flash ADC Design s vylepšeným schématem komparátoru

- Návrh multiplikátoru nízké spotřeby s logickým stylem složeného konstantního zpoždění

- Komparátor dvojitého ocasu s vysokým výkonem a nízkou spotřebou

- Systém Flash Storage s vysokým výkonem v závislosti na vyrovnávací paměti zápisu a virtuální paměti

- Nízký výkon FF založený na přístupu Sleepy Stack

- Optimalizace výkonu LFSR pro BIST s nízkou spotřebou Implementováno v HDL

- Návrh a implementace prodejního automatu s Verilog HDL

- Design akumulátoru založený na generování 3-váhového vzoru s LP-LSFR

- Dekodér Reed-Solomon s vysokou rychlostí a nízkou složitostí

- Rychlejší technika návrhu multiplikátoru Dadda

- Přijímač FM rádia založený na digitální demodulaci

- Generování testovacího vzoru se schématy BIST

- Implementace architektury VLSI pomocí vysokorychlostního kanálu

- Návrh protokolu OCP sběrnice na čipu pomocí funkcí sběrnice

- Konstrukce detektoru fázové frekvence a nabíjecího čerpadla používaná pro vysokofrekvenční smyčku fázového závěsu

- Vyrovnávací paměť a návrh řadiče mezipaměti s VHDL

- ASTRAN založená implementace nízkoenergetických kompresorů 3-2 a 4-2

- Předplacený systém fakturace elektřiny s designem na čipu

- Implementace překrytí pomocí logické buňky a její analýzy výkonu

- Noste pohled dopředu zmije s různými analýzami výkonu bitů pomocí VHDL

- Návrh datové linky s Wi-Fi MAC Protokoly

- Implementace FPGA pro protokol vzájemného ověřování s modulární aritmetikou

- Generování signálu PWM pomocí FPGA a proměnného pracovního cyklu

Projekty v reálném čase

Seznam Projekty VLSI v reálném čase zahrnují hlavně mini projekty VLSI využívající kód VHDL a softwarové projekty VLSI pro studenty inženýrství ECE.

- Pragmatická integrace mezipaměti řádků SRAM do heterogenní 3D architektury DRAM pomocí TSV

- Integrovaná technika autotestu pro diagnostiku poruch zpoždění v klastrových polních programovatelných hradlových polích

- ASIC Návrh komplexního multiplikátoru

- Levná implementace VLSI pro efektivní odstranění impulzního šumu

- Na základě FPGA Prostorový vektor PWM Řídicí IC pro třífázový indukční pohon motoru

- VLSI implementace automatického korektoru a CORDIC algoritmu pro WLAN založené na OFDM

- Automatická extrakce silnic pomocí satelitních snímků s vysokým rozlišením

- Návrh VHDL pro segmentaci obrazu pomocí Gaborova filtru pro detekci nemocí

- Nízko složitá architektura Turbo dekodéru pro energeticky efektivní bezdrátové bezdrátové sítě

- Vylepšení schopností ortogonální konverze kódu pomocí implementace FPGA

- Návrh a implementace pohyblivé řádové čárky ALU

- CORDIC Design pro pevný úhel otáčení

- Kódy produktu Reed-Solomon pro implementaci řadiče Flash NAND na čipu FPGA

- Statistické zlepšení výtěžnosti přístupu SRAM pomocí čtení pomocí obvodů s negativní kapacitou

- Správa napájení síťových rozhraní MIMO v mobilních systémech

- Návrh standardu šifrování dat pro šifrování dat

- Nízká spotřeba energie a oblast efektivního přenášení Vyberte sčítač

- Syntéza a implementace UART pomocí kódů VHDL

- Vylepšené architektury pro jednotku s odčítáním s plovoucí desetinnou čárkou

- 1bitový plně digitální vysílač založený na FPGA využívající modulaci Delta-Sigma s RF výstupem pro SDR

- Optimalizace využití řetězového vyhledávání v dekodéru BCH pro přenos vysoké chybovosti

- Digitální design vysílače DS-CDMA využívající Verilog HDL a FPGA

- Návrh a implementace efektivní architektury systolického pole

- Algoritmus učení dynamiky robotů založený na VLSI

- Všestranný design multimediální funkční jednotky využívající techniku rušivého potlačení výkonu

- Návrh sběrnicového mostu mezi AHB a OCP

- Behaviorální syntéza asynchronních obvodů

- Optimalizace rychlosti modifikovaného dekodéru Viterbi založeného na FPGA

- Implementace I2C rozhraní

- Vysokorychlostní / nízkoenergetický multiplikátor využívající pokročilou techniku potlačení rušivého výkonu

- Upínací virtuální napájecí napětí napájecích obvodů pro aktivní snížení úniku a spolehlivost oxidů brány

- Energeticky efektivní Channelizer založený na FPGA pro softwarově definované rádio

- Architektura VLSI a prototypování FPGA digitálního fotoaparátu pro zabezpečení a autentizaci obrazu

- Vylepšení provozu vnitřního robota

- Návrh a implementace permutační sítě ON-Chip pro multiprocesorový systém na čipu

- Metoda synchronizace časování symbolové rychlosti pro bezdrátové systémy OFDM s nízkou spotřebou

- Řadič DMA (přímý přístup do paměti) pomocí VHDL / VLSI

- Překonfigurovatelné FFT pomocí architektury CORDIC Based Architecture pro přijímače MIMI-OFDM

- Technika potlačení rušivého výkonu pro multimediální / DSP aplikace

- Účinnost kódů BCH ve vodoznaku digitálního obrazu

- Řadič SD-RAM s dvojitou rychlostí dat

- Implementace Gaborova filtru pro rozpoznávání otisků prstů pomocí Verilog HDL

- Návrh praktické redundantní škály nanometrů prostřednictvím vědomé standardní buněčné knihovny pro vylepšenou redundanci pomocí rychlosti vkládání

- Bezztrátový algoritmus komprese a dekomprese dat a jeho hardwarová architektura

- Rámec pro opravu vícebitových měkkých chyb

- Efektivní komprese testovacích dat založená na Viterbi

- Implementace bloků FFT / IFFT pro OFDM

- Waveletová komprese obrazu pomocí VLSI progresivního kódování

- VLSI implementace plně pipelinovaného multiplikátoru, méně 2D DCT / IDCT architektury pro Jpeg

- Emulace chyb na bázi FPGA synchronních sekvenčních obvodů

Jedná se tedy o seznam projektů VLSI pro strojírenství, studenty M.Tech, které jsou užitečné při výběru jejich posledního ročníku projektu. Poté, co jste strávili svůj drahocenný čas procházením tímto seznamem, věříme, že máte docela dobrý nápad vybrat téma projektu podle vašeho výběru ze seznamu projektů VLSI a doufáme, že máte dostatečnou důvěru k převzetí jakéhokoli tématu z seznam. Další podrobnosti a pomoc s těmito projekty nám můžete napsat v níže uvedené sekci komentářů. Zde je otázka, co je VHDL?

Fotografický kredit

- Projekty VLSI od set-tech