Sada instrukcí nebo architektura sady instrukcí je struktura počítače, která poskytuje příkazy pro počítač, které vedou počítač ke zpracování manipulace s daty. Sada instrukcí se skládá z pokynů, režimů adresování, nativních datových typů, registrů, přerušení, zpracování výjimek a architektury paměti. Instrukční sadu lze emulovat v softwaru pomocí tlumočníka nebo zabudovat do hardwaru procesoru. Architekturu sady instrukcí lze považovat za hranici mezi softwarem a hardwarem. Klasifikace mikrokontrolérů a mikroprocesory lze provádět na základě architektury instrukční sady RISC a CISC.

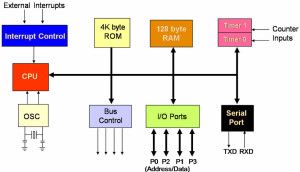

Instrukční sada procesoru

Sada instrukcí specifikuje funkčnost procesoru včetně operací podporovaných procesorem, úložných mechanismů procesoru a způsobu kompilace programů do procesoru.

Co je RISC a CISC?

The RISC a CISC lze rozšířit následujícím způsobem:

RISC představuje počítač se sníženou instrukční sadou a

CISC představuje počítač s komplexní sadou instrukcí.

Architektura RISC (počítač se sníženou instrukční sadou)

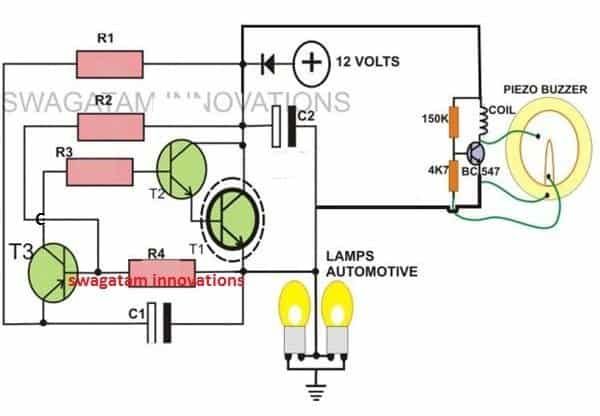

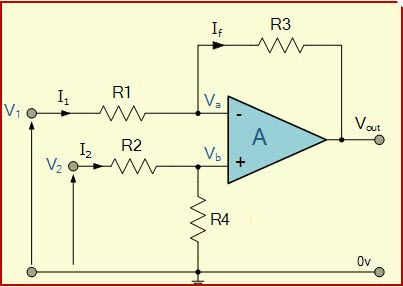

Architektura RISC

The architektura mikrokontroléru který využívá malou a vysoce optimalizovanou sadu instrukcí, se nazývá počítač se sníženou sadou instrukcí nebo se jednoduše nazývá RISC. Nazývá se také jako architektura LOAD / STORE.

Na konci 70. a začátku 80. let byly projekty RISC primárně vyvíjeny od Stanfordu, UC-Berkley a IBM. John Coke z výzkumného týmu IBM vyvinul RISC snížením počtu instrukcí potřebných pro zpracování výpočtů rychleji než CISC. Architektura RISC je rychlejší a čipy potřebné pro výrobu architektury RISC jsou také méně nákladné ve srovnání s architekturou CISC.

Typické vlastnosti architektury RISC

- Technika pipeliningu RISC, provádí více částí nebo fází instrukcí současně tak, aby byla optimalizována každá instrukce na CPU. Proto mají procesory RISC hodiny na instrukci jednoho cyklu, což se nazývá provedení jednoho cyklu.

- Optimalizuje použití registru díky většímu počtu registrů v RISC a většímu počtu interakcí v paměti lze zabránit.

- Jednoduché režimy adresování, dokonce i složité adresování lze provést pomocí aritmetiky AND / NEBO logické operace .

- Zjednodušuje design kompilátoru pomocí identických registrů pro všeobecné účely, což umožňuje použití libovolného registru v jakémkoli kontextu.

- Pro efektivní využití registrů a optimalizaci použití pipeline je zapotřebí omezená sada instrukcí.

- Počet bitů použitých pro operační kód je snížen.

- Obecně je v RISC 32 nebo více registrů.

Výhody architektury procesoru RISC

- Z důvodu malé sady pokynů RISC mohou kompilátoři jazyků na vysoké úrovni vytvářet efektivnější kód.

- RISC umožňuje svobodu využití prostoru mikroprocesory kvůli jeho jednoduchosti.

- Místo použití zásobníku používá mnoho procesorů RISC registry pro předávání argumentů a uchovávání místních proměnných.

- Funkce RISC používají pouze několik parametrů a procesory RISC nemohou používat pokyny pro volání, a proto používají pokyny s pevnou délkou, které lze snadno pipeline.

- Lze maximalizovat rychlost operace a minimalizovat dobu provádění.

- Je zapotřebí velmi menší počet formátů instrukcí (méně než čtyři), několik instrukcí (přibližně 150) a několik režimů adresování (méně než čtyři).

Nevýhody architektury procesoru RISC

- S nárůstem délky instrukcí se zvyšuje složitost, kterou mají procesory RISC provádět, kvůli jejímu cyklu znaků na instrukci.

- Výkon procesorů RISC závisí většinou na kompilátoru nebo programátoru, protože znalost kompilátoru hraje hlavní roli při převodu kódu CISC na kód RISC, proto kvalita generovaného kódu závisí na kompilátoru.

- Při přeplánování kódu CISC na kód RISC, označovaný jako rozšíření kódu, se velikost zvětší. A kvalita tohoto rozšíření kódu bude opět záviset na kompilátoru a také na instrukční sadě stroje.

- Mezipaměť první úrovně procesorů RISC je také nevýhodou RISC, ve kterém mají tyto procesory velké mezipaměti paměti na samotném čipu. K podávání pokynů vyžadují velmi rychlé paměťové systémy .

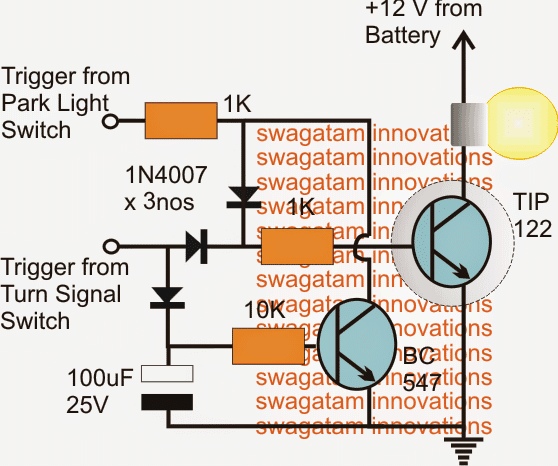

Architektura CISC (Complex Instruction Set Computer)

Hlavním záměrem architektury procesoru CISC je dokončit úkol pomocí menšího počtu montážních linek. Za tímto účelem je procesor vytvořen k provádění řady operací. Komplexní instrukce se také nazývá MULT, která funguje paměťové banky počítače přímo, aniž by kompilátor prováděl funkce ukládání a načítání.

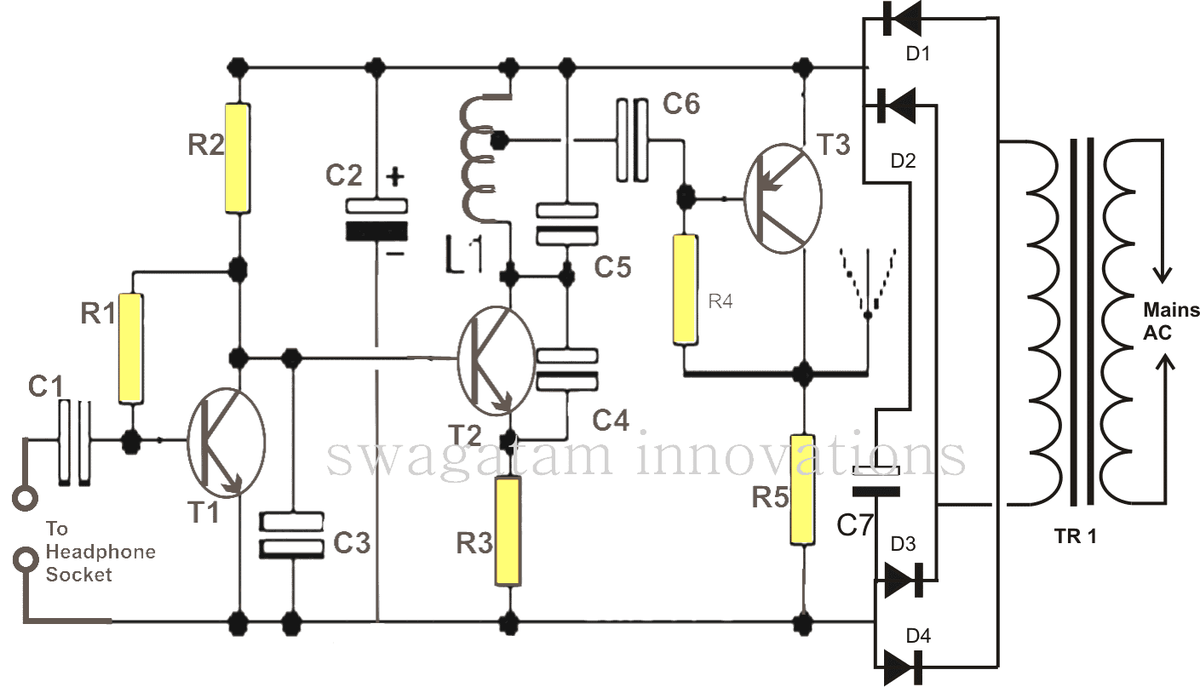

Architektura CISC

Vlastnosti architektury CISC

- Pro zjednodušení architektury počítače podporuje CISC mikroprogramování.

- CISC má více předdefinovaných pokynů, díky nimž je snadné navrhnout a implementovat jazyky na vysoké úrovni.

- CISC se skládá z menšího počtu registrů a většího počtu režimů adresování, obvykle 5 až 20.

- Procesor CISC trvá provádění pokynů různou dobou cyklu - cykly s více hodinami.

- Kvůli složité instrukční sadě CISC je technika pipeliningu velmi obtížná.

- CISC se skládá z většího počtu pokynů, obvykle od 100 do 250.

- Speciální pokyny se používají velmi zřídka.

- S operandy v paměti se manipuluje podle pokynů.

Výhody architektury CISC

- Každá instrukce strojového jazyka je seskupena do instrukce mikrokódu a odpovídajícím způsobem provedena a poté jsou uloženy v paměti hlavního procesoru, označované jako implementace mikrokódu.

- Vzhledem k tomu, že paměť mikrokódu je rychlejší než hlavní paměť, lze instrukční sadu mikrokódu implementovat bez významného snížení rychlosti oproti implementaci s pevným připojením.

- Celá nová sada instrukcí může být zpracována úpravou designu mikro programu.

- CISC, počet instrukcí potřebných k implementaci programu lze snížit vytvořením bohatých instrukčních sad a lze jej také efektivněji využívat pomalou hlavní paměť.

- Díky nadmnožině pokynů, která se skládá ze všech dřívějších pokynů, je mikrokódování snadné.

Nevýhody CISC

- Množství času, který zabere různé pokyny, se bude lišit - z tohoto důvodu se výkon stroje zpomaluje.

- Složitost instrukční sady a hardware čipu se zvyšuje, protože každá nová verze procesoru se skládá z podmnožiny dřívějších generací.

- Pouze 20% stávajících instrukcí se používá v typické programovací události, i když existuje mnoho specializovaných instrukcí, které se ani často nepoužívají.

- Podmíněné kódy jsou nastaveny instrukcemi CISC jako vedlejší účinek každé instrukce, která vyžaduje čas pro toto nastavení - a jak následná instrukce mění bity podmíněného kódu - tak musí kompilátor prozkoumat bity podmíněného kódu, než k tomu dojde.

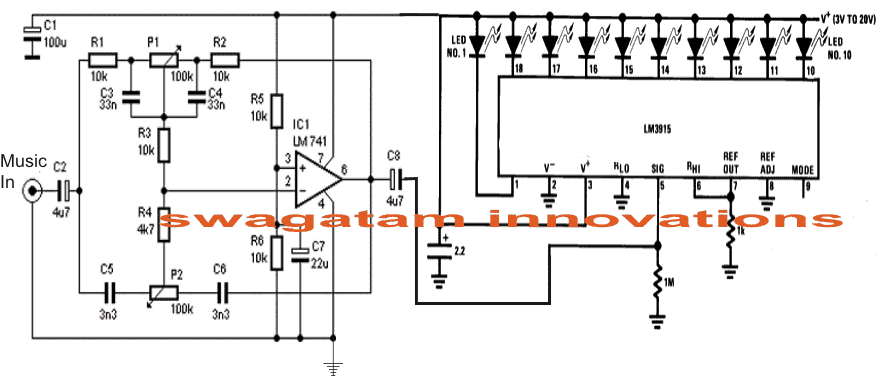

RISC vs. CISC

- Programátorům lze zabránit plýtváním odstraněním nepotřebného kódu v RISC, ale při použití kódu CISC to vede k plýtvání cykly kvůli neefektivnosti CISC.

- V RISC je každá instrukce určena k provedení malého úkolu tak, že k provedení složitého úkolu se používá více malých instrukcí společně, zatímco k provedení stejného úkolu pomocí CISC je zapotřebí pouze několik instrukcí - protože je schopna provádět složitý úkol protože pokyny jsou podobné vysokojazyčnému kódu.

- CISC se obvykle používá pro počítače, zatímco RISC se používá pro chytré telefony, tablety a další elektronická zařízení.

Následující obrázek ukazuje další rozdíly mezi RISC a CISC

RISC vs. CISC

Tento článek tedy pojednává o vlastnostech architektur RISC a CISC architektury procesorů RISC a CISC výhodách a nevýhodách RISC a CISC a rozdílech mezi architekturami RISC a CISC se stručným nápadem. Další informace týkající se architektur RISC a CISC naleznete v níže uvedených komentářích.

Fotografické kredity:

- Instrukční sada procesoru od arstechnica

- Architektura RISC od lsi-soutěž

- RISC vs. CISC podle csarassignment